# How Motion Control Enables Modern Datacom Technologies

Business Development Manager

jbressi@aerotech.com

linkedin.com/in/justinbressi

#### Macro Trends Driving Datacenter Growth

- Modern applications like artificial intelligence (AI) & high-performance computing (HPC) are driving compute demands that outpace Moore's Law

- Bandwidth needs are following a similar trajectory

- Scaling of established technologies is beginning to see diminishing returns

- Paradigm-shifting technologies such as silicon photonics (SiPh) & advanced packaging are key to addressing these requirements

#### Silicon Photonics Offers Key Advantages

Increasing level of photonics integration provides improvements in key areas:

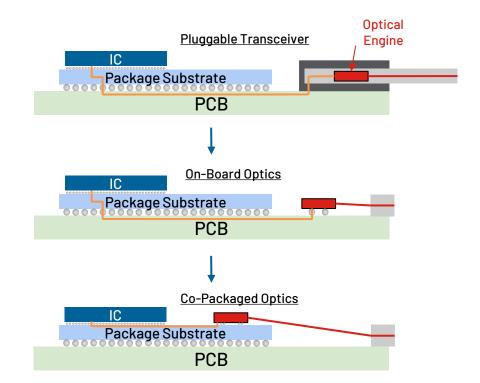

## **Optical Integration Scaling**

- The industry continues to pursue higher levels of integration

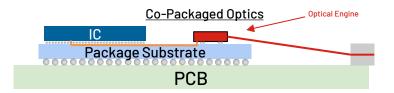

- Advanced packaging techniques enable co-packaging optical engine with electronic integrated circuits (EICs)

- Tighter integration will continue to drive performance improvements

#### Increased Complexity = New Challenges

- Tighter integration requirements present new manufacturing, test & packaging challenges, particularly at scale

- Quality control in all stages of manufacturing is critical

- Precision at micrometer & even nanometer levels is often required

#### **Photonic Device Precision Processes**

**Component Manufacturing & Test**

Advanced Packaging

**Device Assembly & Test**

Wafer- & Die-level Test

Precision Alignment for Heterogeneous Integration & Chip Stacking

Optical Alignment & Assembly

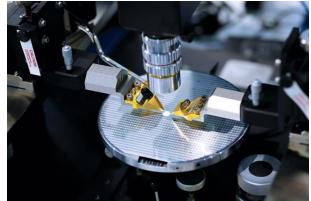

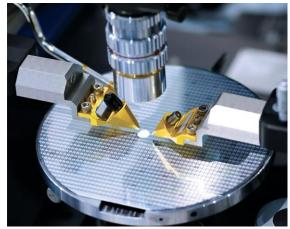

#### Wafer- & Die-level Test

- While SiPh-based PICs are manufactured using many of the same techniques as traditional EICs, test methodologies are significantly more complex

- In addition to electrical connections, optical paths need to be tested, introducing much different requirements

Dual-sided optical testing of photonic device

Wafer-level testing

**Component Manufacturing & Test**

Advanced Packaging

# Silicon Photonic Wafer Probing

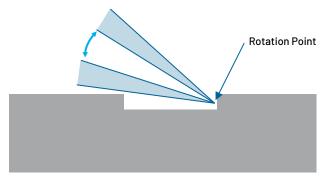

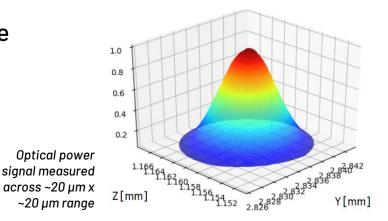

Successful wafer-level edge coupling of fiber arrays in a trench depends on optical positioning sensitivity & device-under-test (DUT) geometry

Diagram showing wafer-level edge coupling in trench

Component Manufacturing & Test

Advanced Packaging

**Device Assembly & Test**

Proprietary and Confidential

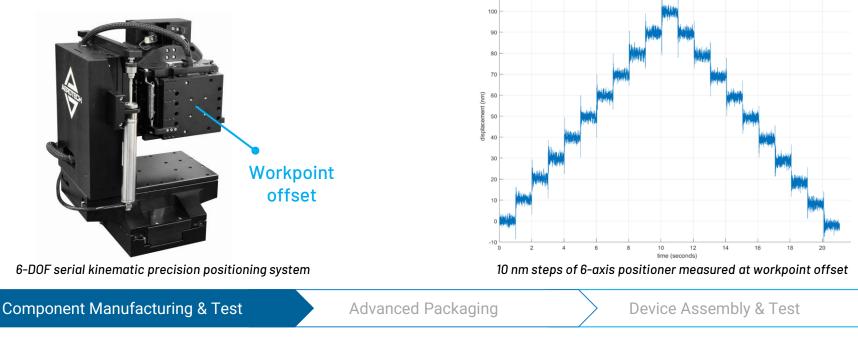

Positioning system pivoting about assigned work point

# Silicon Photonic Wafer Probing

• Crossed-roller bearing stages combine industrial robustness with high stiffness, nm-level in-position stability & step size

#### **Advanced Packaging**

- Advanced packaging techniques are inherently required to integrate PICs with traditional EICs

- Emerging technologies like copackaged optics (CPO) continue to drive requirements for improved precision without sacrificing throughput

• These processes often require µmor nm-level sensitivities

**Component Manufacturing & Test**

Advanced Packaging

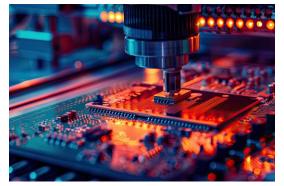

# 2.5D & 3D Stacking

- Advanced packaging techniques like 2.5D and 3D stacking are used for heterogeneous integration

- Vertically stacking chips, wafers, interposers and other devices requires high precision to align critical features

- Processes must combine high yield and high throughput, both of which are enabled by precise and high-dynamic motion control

Precision pick-and-place for device packaging

Advanced Packaging

#### Heterogeneous Integration

#### **Co-packaging EICs & PICs**

- Methods like fan-out wafer-level packaging (FOWLP) have already been deployed for co-packaging

- Scalability remains a key challenge for heterogeneous integration processes

- Emerging methods like micro-transfer printing are being explored to increase throughput via parallel processing

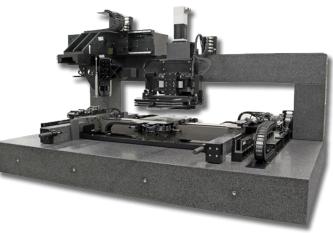

10-DOF motion platform on granite for planaritysensitive alignment

Advanced Packaging

# **Alignment for Device Assembly**

- Alignment processes for device-level assembly also require high precision, often in many degrees of freedom

- µm-level optical misalignments can create unacceptable levels of insertion loss

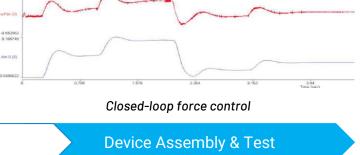

- Maintaining precise positioning during bonding processes can require closedloop position & force control

**Component Manufacturing & Test**

Advanced Packaging

# **Alignment for Device Assembly**

- Aligning components simultaneously requires multi-axis coordination

- Linear motor technology enables high dynamics with µm- and nm-level precision

- High-bandwidth force control loops ensure appropriate forces are applied during assembly

10+ DOF motion platform for optical device packaging

0.049063

**Component Manufacturing & Test**

Advanced Packaging

#### Conclusion

Precision automation is critical to modern datacom infrastructure.

- Amplified by macro trends like AI & HPC, demand for data center bandwidth is increasing exponentially

- Paradigm-shifting technologies will be fundamental to addressing this demand

- Precision motion control is playing an increasingly important role in the manufacture & test of these technologies

#### **Questions?**