Jean-Luc POLLEUX CTO & co-founder, ICON Photonics Former Professor, ESIEE Paris, Univ-Eiffel, ESYCOM-CNRS

### "Scalable Packaging of PIC Exploiting Wafer-level Optical and Electrical Interconnects"

EPIC Workshop on « PIC Postprocessing and Packaging », Laser World of Photonics, Munich, 2023 June 29th

### About us

- Technological independent SME created in 2018

- Offices and Clean Room Facilities in France, Paris region

10 Headcounts - **Strong R&D** > 50% PhD in Photonics

Spinoff of CNRS research center

- 10+ years of R&D in microfabrication and photonics integrated packaging

- 650m<sup>2</sup> cleanrooms production-line (Class 100) platform

- Licensing agreement worldwide with exclusivity including 6 patents

Mission: develop and commercialize fiber-to-the-chip connectivity solutions enabling the next generation optical and quantum applications

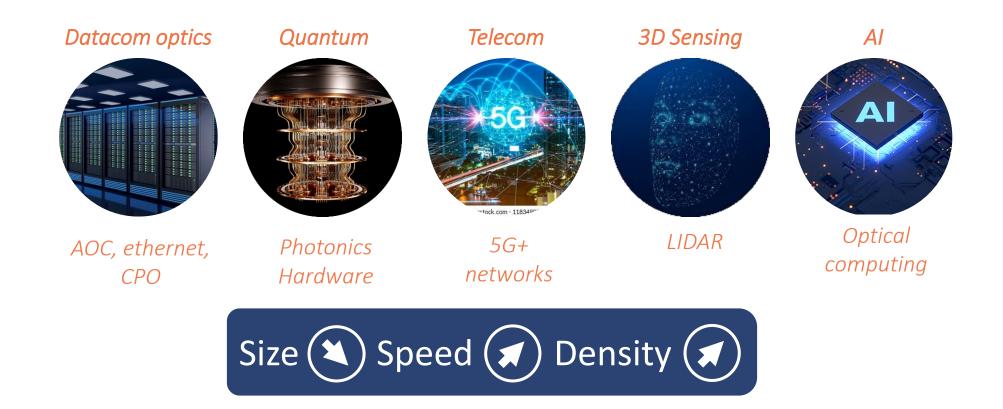

## Market drivers

**Pluggable Optics**

#### **Co-Packaged Optics (CPO)**

**CPO to 3D-chiplet**

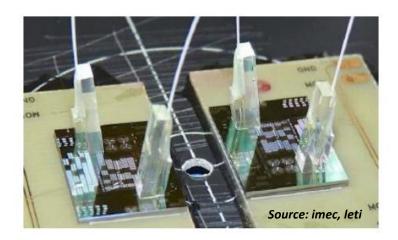

IMEC Si-PIC platform

Ranovus 2021, nx100Gbps PAM4

- Integration: key to lower cost and higher density

- Speed: get smaller to get higher data rates

- + Scalable and Cost-efficient model: <100\$ per 100Gbit/s

- Efficiency: save energy and save photons

- + Going above the 98% efficiency

- Getting light In and Out of the chip with a new standard at wafer-level

### **Optical Interconnects applications**

Among these markets, PIC are moving up very rapidly. Quantum market itself is putting needs with 10000+ wafers per year in 2026+ for large size PICs

## **PIC challenges**

### • PIC to fiber edge-coupling

- Exhibiting intrinsic ultra low losses

- Quantum applications are looking toward losses <0.1dB (T-98%)

- 5G/6G or Datacom/Telecom: any 0.5dB saves 1dB electrically

- Intrinsic low losses are not the only challenge, you need to ensure about the worst-case losses after managing the attachment and reliability tests to guarantee <0.5dB</li>

- Alignment tolerance is the key challenge with MFD 3-9 $\mu$ m (time/performance)

| Т(%) | A(dB) | Gom(dB) |

|------|-------|---------|

| 1%   | -20   | -40     |

| 10%  | -10   | -20     |

| 50%  | -3.0  | -6      |

| 70%  | -1.5  | -3      |

| 80%  | -1.0  | -2      |

| 90%  | -0.5  | -1      |

| 93%  | -0.3  | -0.6    |

| 95%  | -0.2  | -0.4    |

| 98%  | -0.1  | -0.2    |

| 100% | 0     | 0       |

## **PIC challenges**

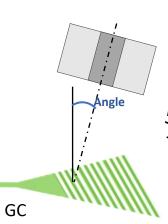

- PIC to fiber vertical coupling through Grating Couplers

- Controlling angles (wavelength, temperature)

- Mechanical fiber holder fixture on the wafer

SMF/MMF

5° to 15° with  $\lambda(T)$ Target <0.5dB losses over 50nm<sup>+</sup>

## **PIC challenges**

- PIC to PIC free-space links

- Smaller PICs to reduce the development cycles / increase the yield

- Choice on the platform of integration / tolerance of alignment

=> Short distance links (<1-3mm)

- LiDAR and free-space launch:

- Small pitchs for the emission/reception:  $30\mu m 127\mu m$

- PIC mmw-interface to drivers and FPGA/ASIC

- Bandwidth >60GHz to address >112Gbps/224Gbps

## **ICON Photonics Technology**

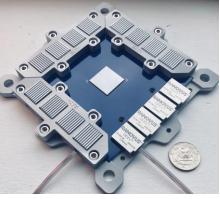

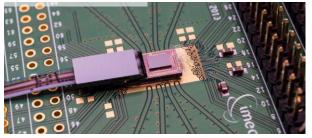

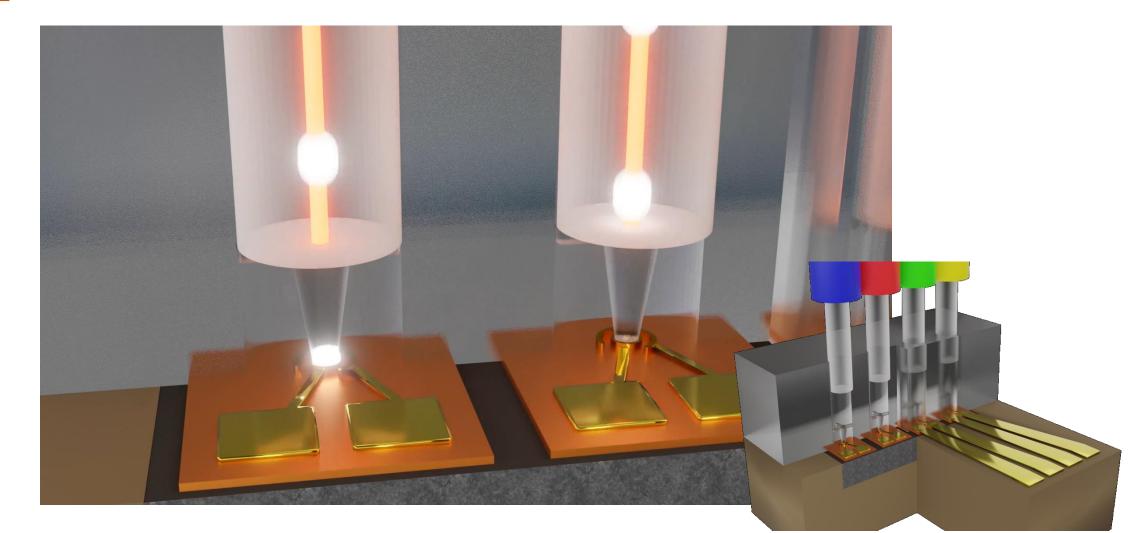

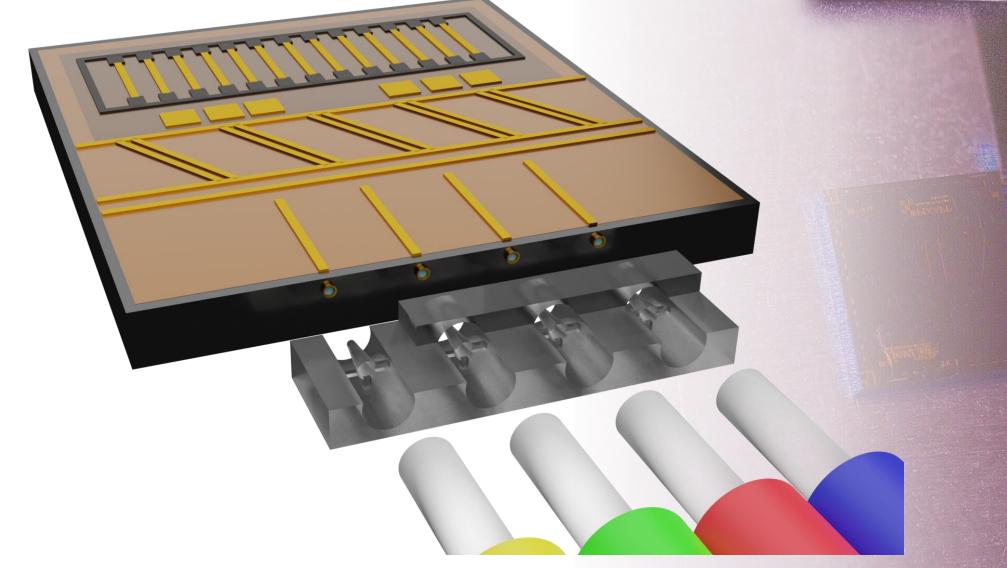

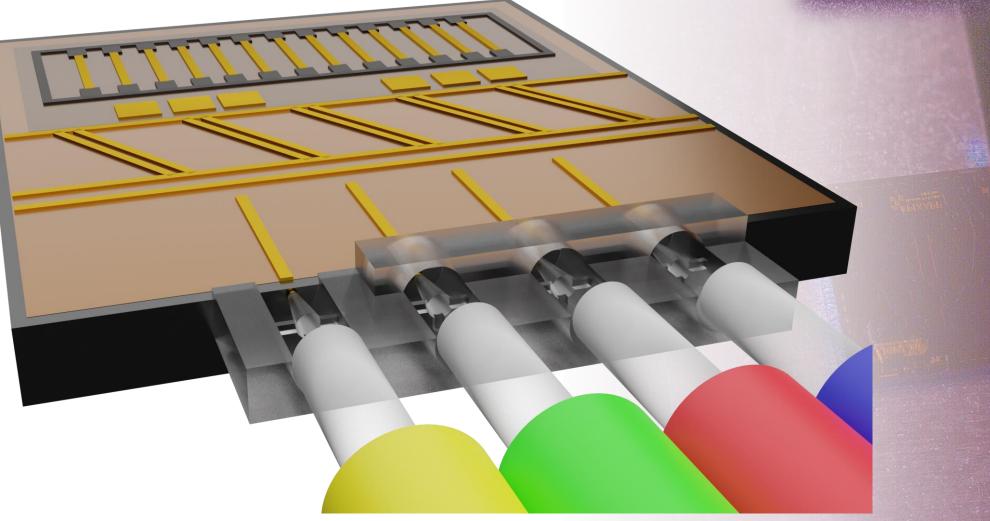

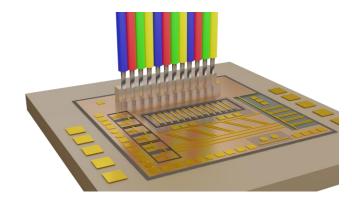

### All-in-one-package: Photonics + Electronics + Mechanics integration

### Focus on PIC to fiber coupling

And which the second

### Focus on PIC to fiber coupling

## PIC to PIC / PIC to free-space

PHOTONICS

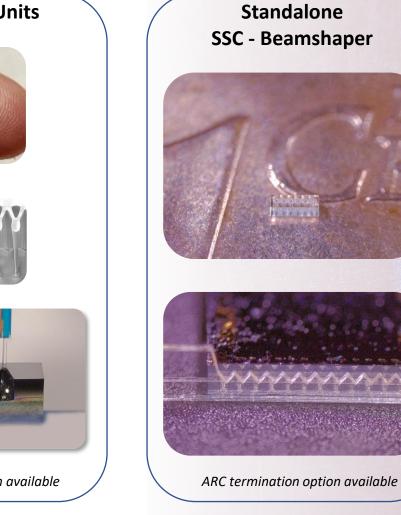

### Ultra-low-loss coupling solutions as a service

#### Surface I/O array

MMF, SMF, MCF Top / back-side PD, VCSEL, GC-PIC (<0.5), SNSPD, TES Both silicon interposer and full-wafer possibilities

#### Edge I/O array

EEL, DFB, DBR, Edge-PIC SSC, MMF, SMF Both Silicon interposer and standalone possibilities

Surface to Edge I/O array

Upcoming

#### SMF and MMF

Coupling loss <0.1dB 70μm to 10μm (MMF) 50μm to ~1μm (SMF/MCF) Fiber holder with passive alignment

#### SMF

Coupling loss <0.5dB Active alignment (standalone) Passive alignment (clipping option)

#### Advantage of surface I/O array

For all : - Zero-Air-Gap option or ARC - Si interposer up to mmw

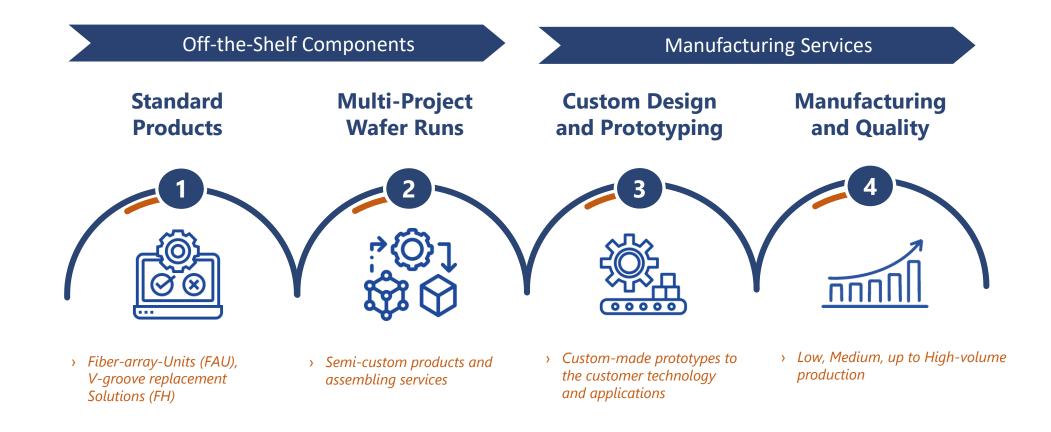

## Off-the-shelf product offer

PHOTONICS

FH + SUSS

## We design and produce for you

### **One-stop-shop from design to industrialization**

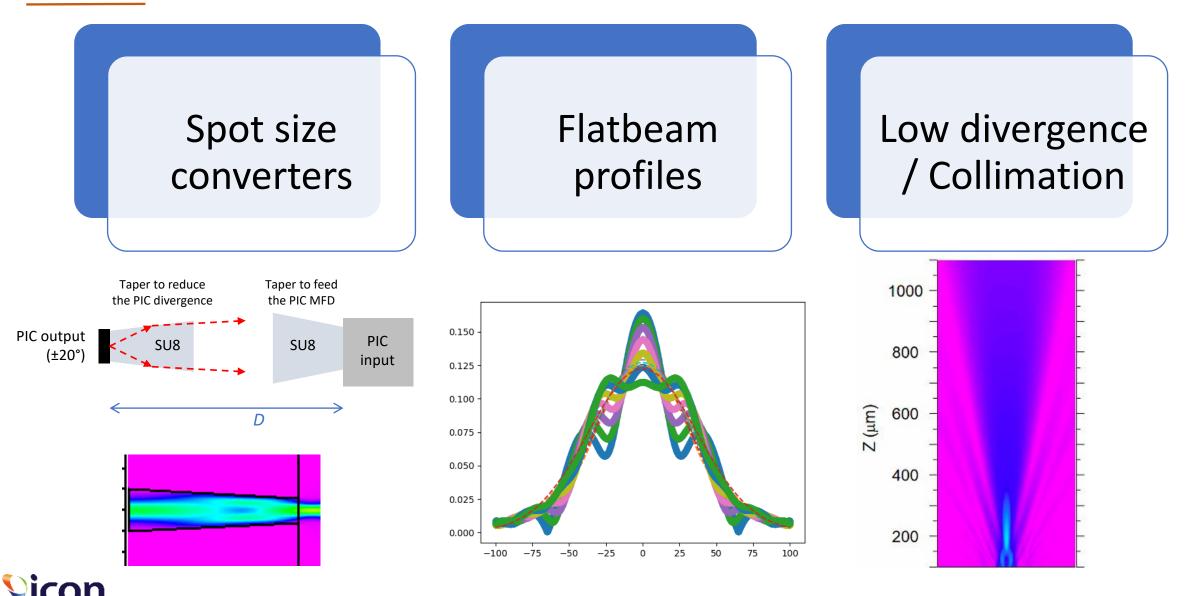

# Thin-film Polymer Benefits?

### **Optical Properties**

- > High transparency (from 500nm up to 5μm)

- Low coupling losses (<0.5 dB and <0.1dB)</li>

- > ARC compatible / Fiber refractive index continuity

### **Cost effectiveness**

- Material

- > Wafer-level process

- > UV mask lithography

### Versatility

- > Contact mask design

- > Monolithic and hybrid options

### From °mK cryogenic to high-temp >350°C conditions

#### EPIC Workshop – PIC Postprocessing and Packaging – June 29th, LWoP, 2023

### Reliability

- > Telcordia compliance

- > Mechanical stability

- > Chemically resistant

- > Thermal stability

- > Cryogenic temperatures <100mK

- > Reflow compatible up to >350°C

### Mechanical properties

- > High aspect ratio

- > Adhesion & Bonding

- > Biocompatibility

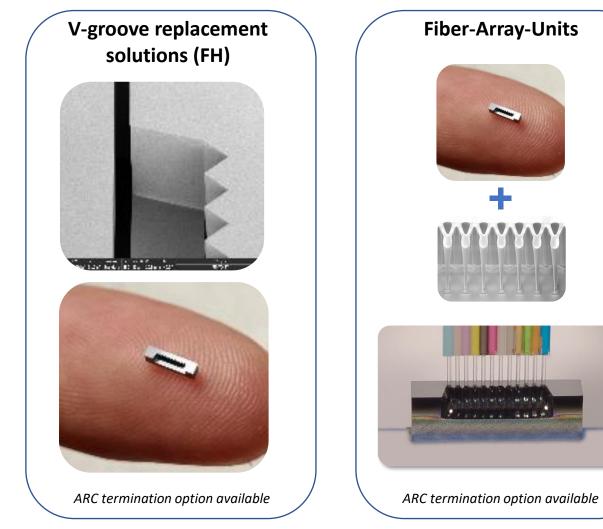

## Invitation to visit ICON Photonics @ECOC 2023

ECOC 2023

Glasgow, Scotland October 2023

### 2-4 October 2023, Booth #830

- Showcase of products and services

- Fiber Array Units (FAU)

- V-groove replacements (FH)

- Chip to Fiber Interconnects

- Si-interposer solutions

PHOTONICS

www. icon-photonics.com

## Thanks

jean-luc.polleux@icon-photonics.com