PDKs of the future – Enabling a modular design ecosystem

Pierre Wahl

EPIC TechWatch - ECOC

#### **Luceda Photonics**

Help photonic IC designers enjoy the same **first-time** right experience as electronic IC designers "

# **IPKISS Photonics Design Platform**

### Level 1

1 Design

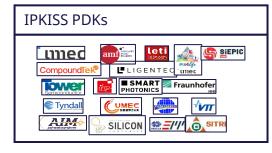

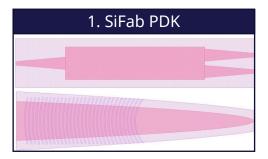

#### IPKISS PDKs

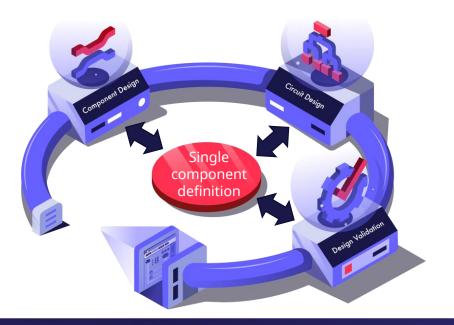

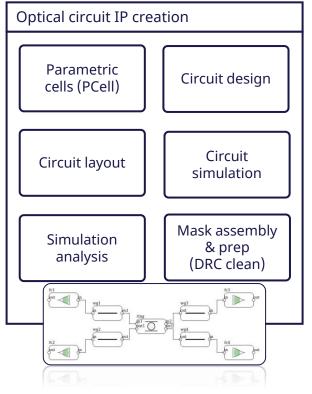

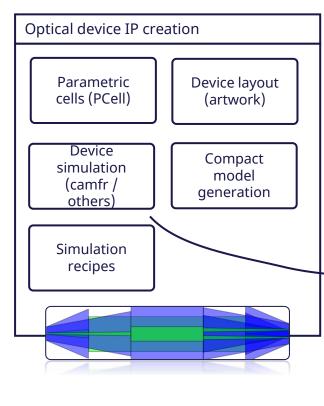

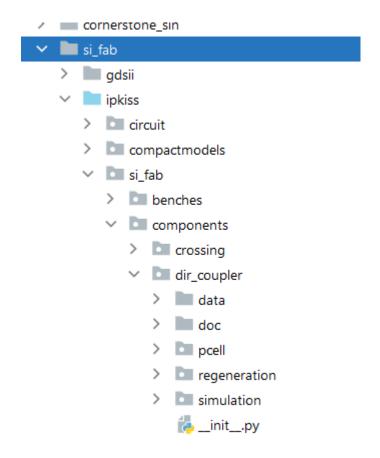

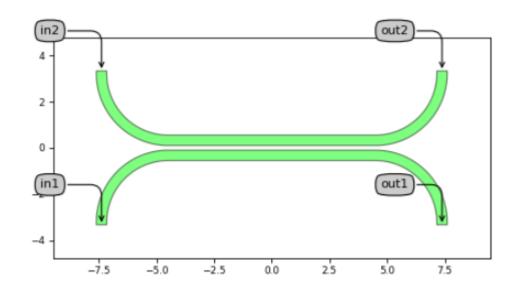

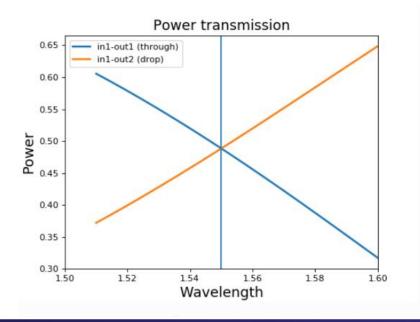

- Power of IPKISS: layout + models + simulation

- Python-based PDK for maximum flexibility

- Automated testing and quality assurance

- Export to OpenAccess, iPDK, uPDK standards

- Vast offer of PDKs from around the world

# Level 2

1 Design

#### What are our customers doing?

4 – Remote repository

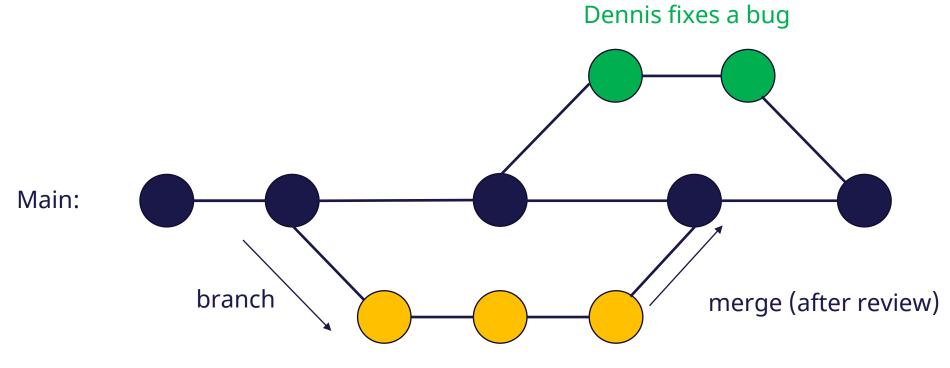

#### Version control

Chiara works on a new feature in a different branch

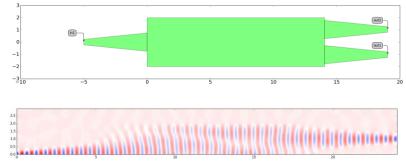

# Example – Directional coupler

#### Level 3

- Packaging Foundries

- Interposers

- Design Houses

- Heterogeneous Integration

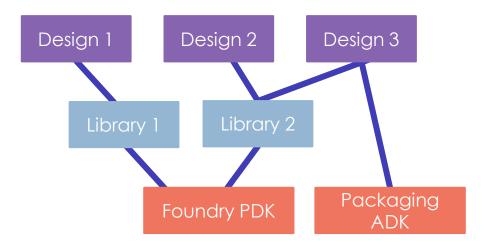

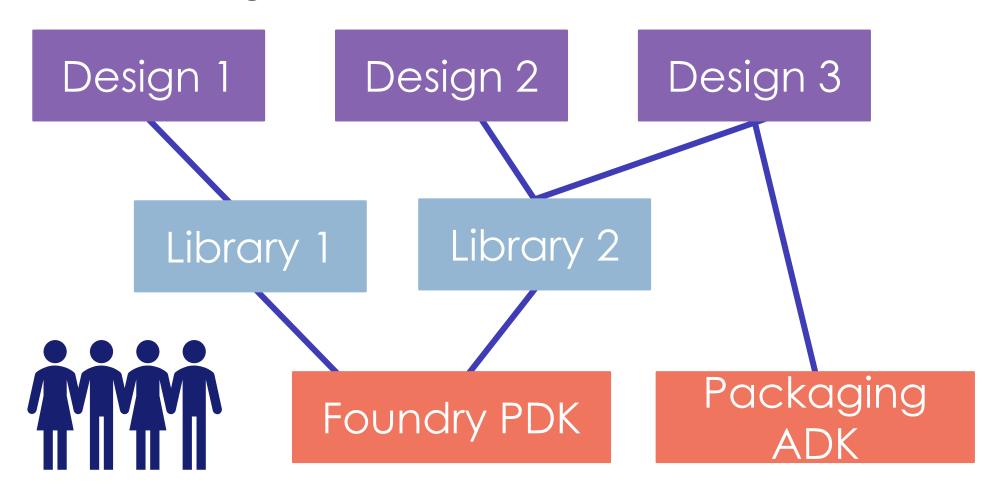

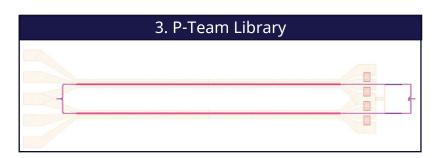

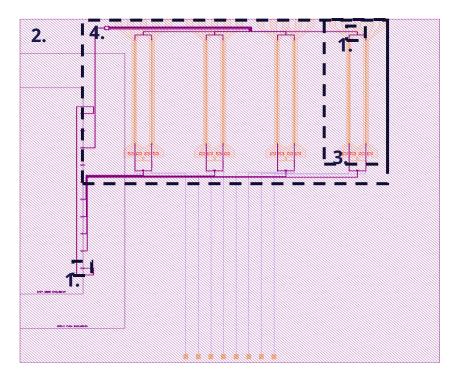

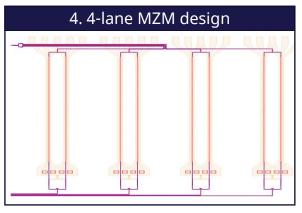

#### PDKs and ADKs

from si\_fab import all as pdk from tyndall\_packaging.all import UniformPackagingArray

#ADK x #PDK = 50 combinations?

Parametric circuits makes it possible to separate both.

PIC Foundries Build and Maintain PDK Packaging Foundry

#### Conclusion

1 – Library development

### **IPKISS IP Management**

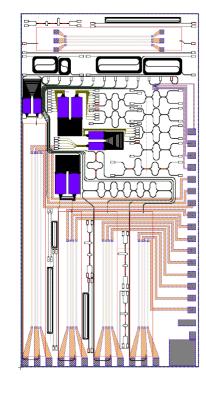

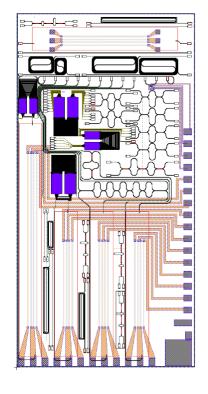

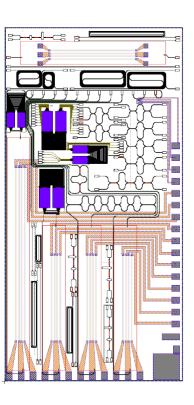

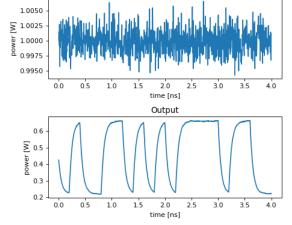

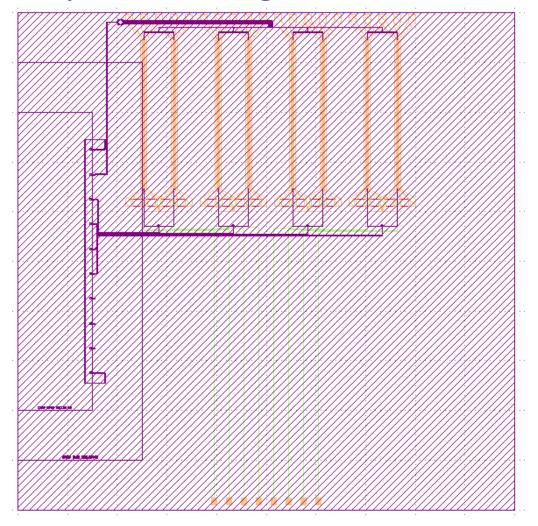

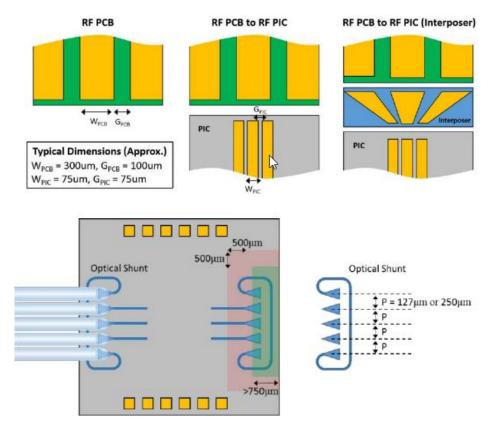

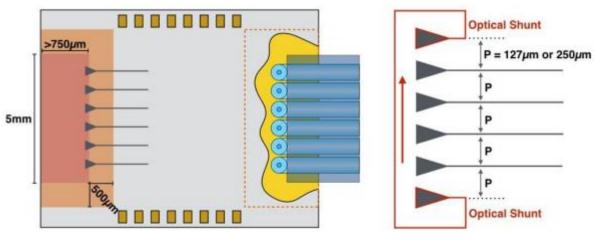

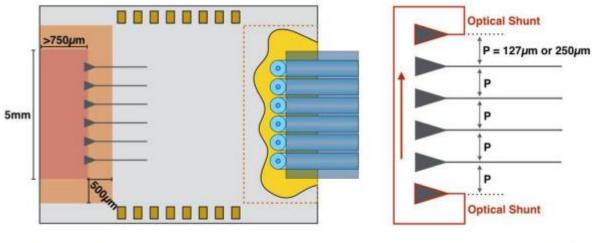

# Example 2: Packaged 4-Lane Modulator

# Respect the packing foundry rules

```

from si_fab import all as pdk

from tyndall_packaging.all import UniformPackagingArray

packaging_arrray = UniformPackagingArray(

n_o_user_west_gratings=8,

n_o_user_east_gratings=1,

n_o_north_bondpads=10,

n_o_south_bondpads=8,

bondpad=pdk.BondPad(metal1_size=(50, 70), metal2_size=(50, 70)),

grating=pdk.FC_TE_1300(),

)

packaging_array_lv = packaging_arrray.Layout()

packaging_array_lv.write_gdsii("sifab_chip_package_oband.gds")

```

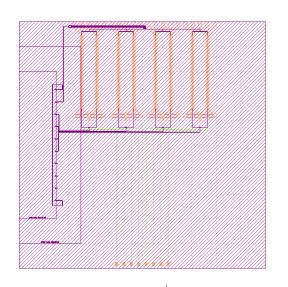

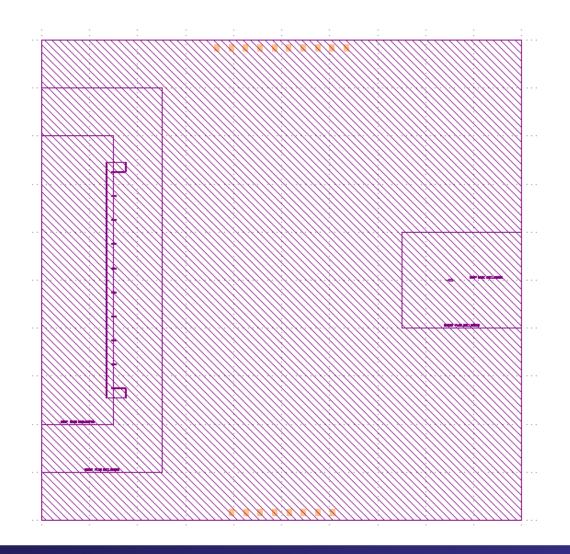

# Respect the packing foundry rules

```

from si_fab import all as pdk

from tyndall_packaging.all import UniformPackagingArray

packaging_arrray = UniformPackagingArray(

n_o_user_west_gratings=0,

n_o_user_east_gratings=1,

n_o_north_bondpads=10,

n_o_south_bondpads=8,

bondpad=pdk.BondPad(metal1_size=(50, 70), metal2_size=(50, 70)),

grating=pdk.FC_TE_1300(),

)

packaging_array_lv = packaging_arrray.Layout()

packaging_array_lv.write_gdsii("sifab_chip_package_oband.gds")

```

Instance causing the error:

<UniformPackagingArray PCell

'TYNDALL\_PACKAGE\_1'>

Cause of the error: You can't have only 1 grating on your chip.

Properties causing the error:

n\_o\_user\_east\_gratings --> 1

n\_o\_user\_west\_gratings --> 0

Process finished with exit code 1

## Respect the packing foundry rules

```

from si_fab import all as pdk

from tyndall_packaging.all import UniformPackagingArray

packaging_arrray = UniformPackagingArray(

n_o_user_west_gratings=0,

n_o_user_east_gratings=1,

n_o_north_bondpads=10,

n_o_south_bondpads=8,

bondpad=pdk.BondPad(metal1_size=(50, 70), metal2_size=(50, 70)),

grating=pdk.FC_TE_1300(),

)

packaging_array_lv = packaging_arrray.Layout()

packaging_array_lv.write_gdsii("sifab_chip_package_oband.gds")

```

Process finished with exit code 1

#### Sources

## What can we do for you? What can you do for us?

- O Designers get a state-of –the-art design solutions

- Well maintained IP

- Managed dependencies

- Rapid iterations

- Supply chain partners get to

- Focus on their core added value

- Maintain and distribute their added value without comprising business logic

- In an open environment ready to integrate with others.

- Talk to us:

- Technical specification

- Business logic

# We are hiring!

#### Open positions

Sales engineer

Application engineer

Apply

Luceda People | Chiara: Science and core skills, a powerful combination

Chiara, who works as a Marketing, Sales & Application Engineer, appreciates the diversity her job entails. In additional to technical work, Chiara is also responsible for sales and marketing, which tu...

Read interview

#### Connect with us on LinkedIn

Connect with Pierre

Connect with Joris

**Connect with Chiara**