Monolithic Integration of Photonics and Electronics for High-Capacity Co-Packaged Optical Engines

### Georg Röll

### Outline

## RANOVUS

#### What is Co-Packing?

- □ What are some Co-Packaging Applications?

- Technology Platform for Monolithic EPIC SOC Integration

- End-to-End Transmission Model

- IBIS-AMI Optical Re-Driver Model

#### What did we build?

- □ Odin<sup>™</sup>8P EPIC, ILS Version Key Functional Blocks

- □ Ring Resonator Modulator (RRM)

- □ 100G Tx Macro (DRV+RRM)

- 100G Rx Macro (PD+TIA)

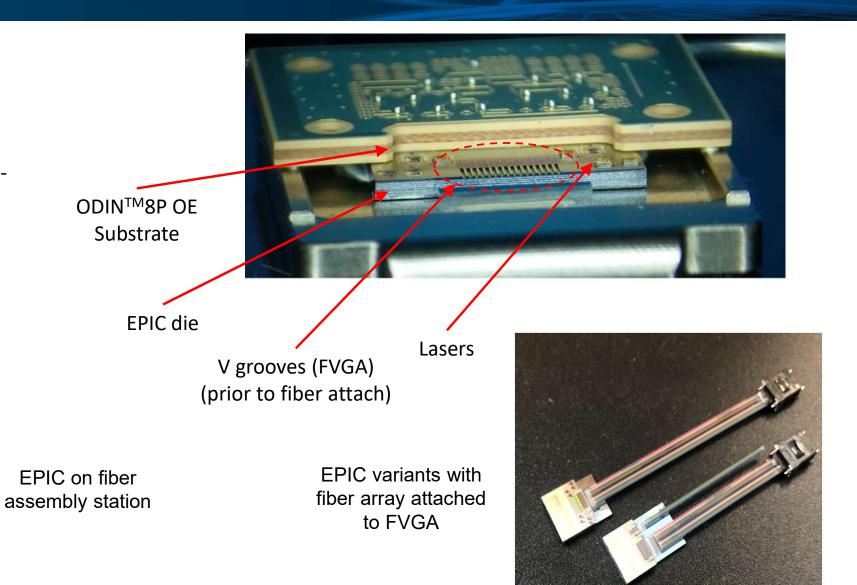

- □ ODIN<sup>™</sup> EPIC Fiber Attach & Packaging

- □ O-Band Lasers for EPIC Integration

- What did we demonstrate at OFC?

- Test results

# RANOVUS

## What is Co-Packaging?

ASIC

Host PCB

**Co-Packaged Assembly Substrate**

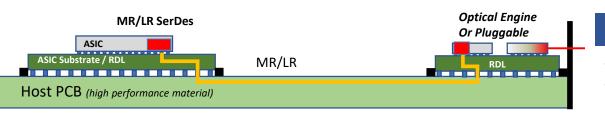

- Pluggable module at the front panel or on-board module

- SerDes I/F can support pluggable or on-board optics

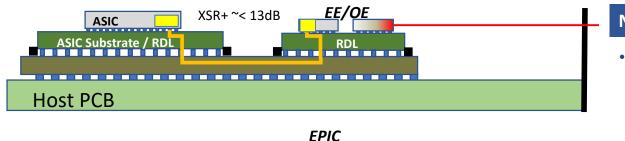

#### **Co-Packaging Architectures**

- The Co-Packaging Assembly (CPA) is a Multi-Chip Module (MCM) with either socketed or soldered

- XSR SerDes I/F supports ~50mm reach across substrate and saves SerDes electrical interface power which translates up to ~40% reduction in Ethernet switch card power

Substrate

socketed

#### Near Packaging Architectures

ASIC may be packaged and mounted on a high-quality platform (HDI)

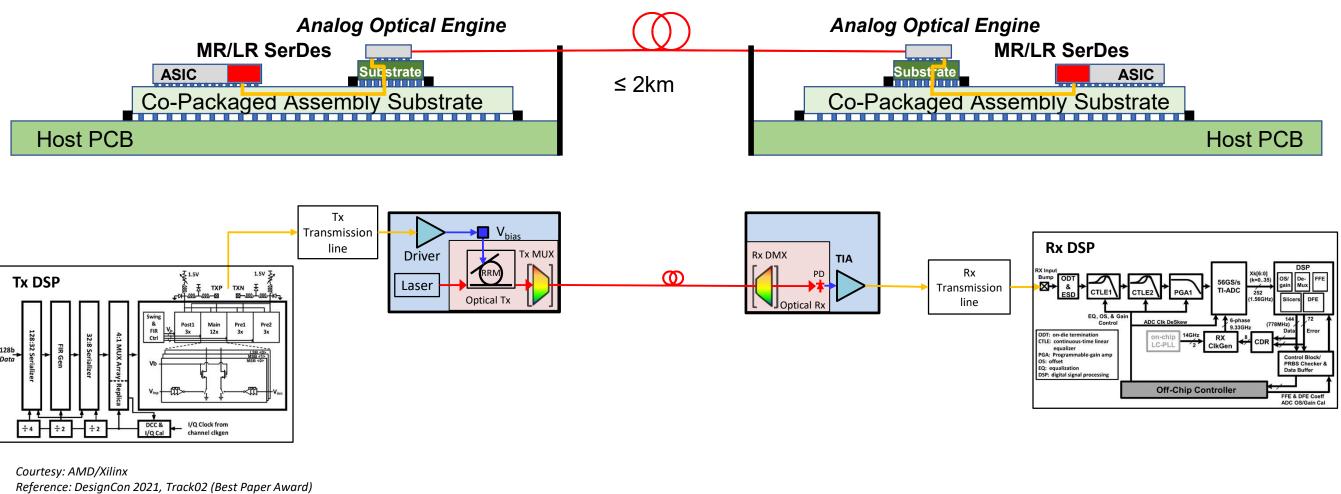

- A MR/LR SerDes can directly drive a non-retimed co-packaged optical engine

- This allows early co-packaging with ASICs which have only LR or MR type SerDes

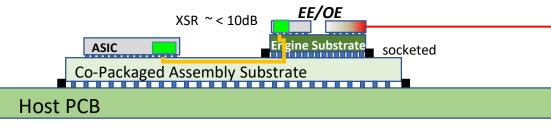

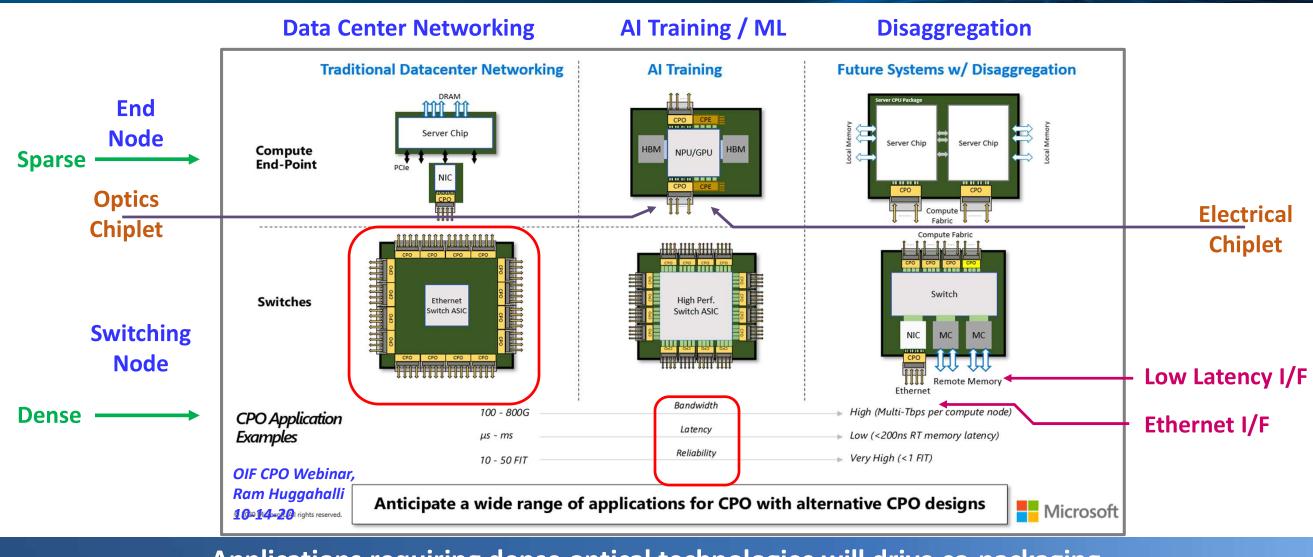

## What are some Co-Packaging Applications?

## RANOVUS

#### Applications requiring dense optical technologies will drive co-packaging

## Technology Platform for Monolithic EPIC SOC Integration

# RANOVUS

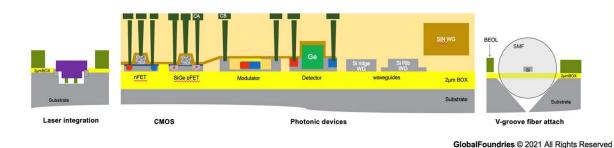

#### **GF 45SPCLO SiPh Foundry Offering** Technology Overview

- High performance photonic passive and actives device library

- Monolithic integration of high performance 45nm RF SOI CMOS

- Dual SOI thickness: 160nm photonics, 88nm CMOS; 2µm BOX, SOI and SiN waveguides

- State-of art 300mm Fab8 Malta Fab, leveraging advanced immersion lithography

- Freeform design enabled with curve-linear GDS with advanced OPC

- Passive v-groove fiber array / attach, 250µm, 127µm pitch

- State-of-Art PDK enablement with EO co-design environment, standard cell digital library

- Automated electrical / optical wafer level test

Global Foundries material courtesy of Vikas Gupta

#### Beside using foundry PDK, Ranovus owns or co-develops critical IP:

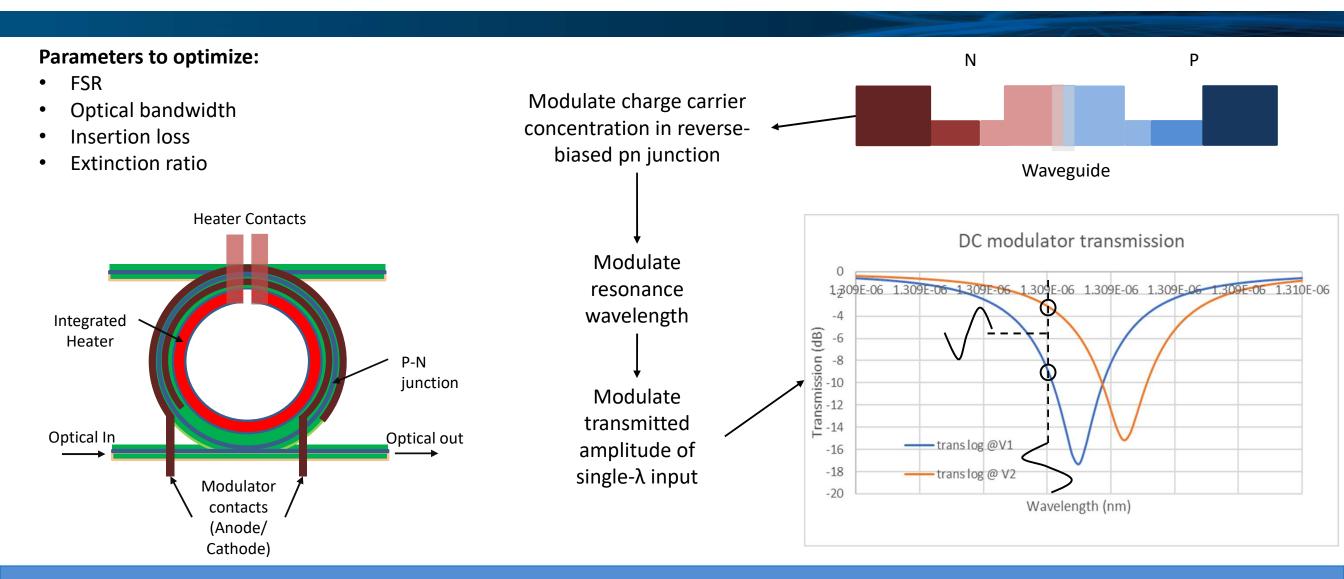

- Ring resonator modulator (RRM)

- Lasers & laser attach design / process

- Fiber assembly process

- All electronic designs, including RF building blocks and control IP

#### **Benefits:**

- Enables a true opto-electronic system-on-chip

- Smallest possible size of a solution, as all functional blocks are on single die

- Simplified packaging (no complex 3D packaging etc.)

- Super low-parasitic interconnect between photonic and electronic (modulator driver modulator, Photodetector transimpedance amplifier)

- No impedance matching required

- Enables best-in-class power dissipation

- Enables superior TIA noise performance and bandwidth

- SOI prevents substrate coupling and X-talk

#### **Challenges:**

- BOX related thermal limitations need to be taken into account in circuit design

- No metal allowed in close vicinity of optical waveguides

- Routing constrained, as only upper metal layers can be used to cross WG

- Narrow Si WG have non-negligible insertion loss, should be kept as short as possible

- Placement & routing constrained

### Ranovus chose Global Foundries' 45nm Process 45SPCLO as the optimum EPIC integration platform

## End-to-End Transmission Model

## RANOVUS

"End-to-end IBIS-AMI Modeling and Simulations of Electrical/Optical Links"

**Transmission Model for End-to-End Link Simulation**

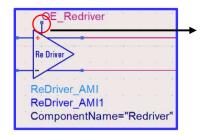

### **IBIS-AMI** Optical Re-Driver Model

# RANOVUS

#### **Compiled version of Matlab model**

- Purpose: Co-simulation of complete electrical-optical-electrical (EOE) chain with packaged Serdes model and s-parameters

- EOE re-driver model variables

- □ RRM Detuning Frequency (Hz)

- □ Channel Loss (dB)

- □ LaserPower

- Gain (dB)

- Configuration

- Modulation

- ModType

- DesignType

- □ DRVType

- □ bePlot

- Debug

#### Re-Driver symbol for ADS simulator

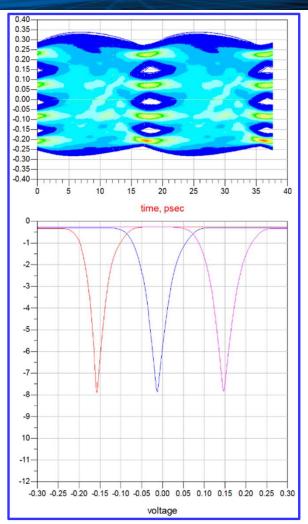

Example: output waveform from IBIS-AMI simulation with Re-Driver model

## What did we build?

# RANOVUS

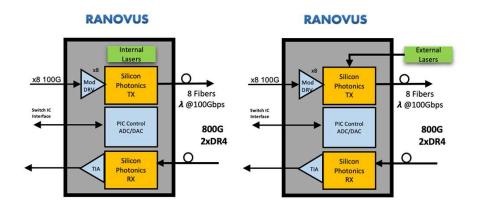

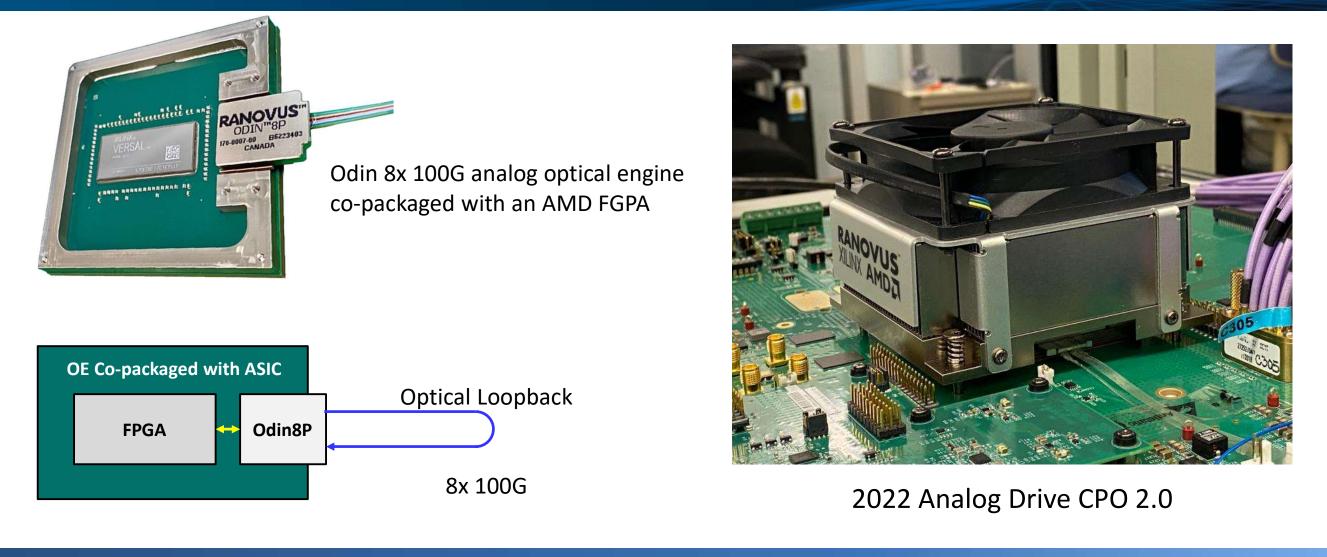

- Analog Optical Engine (AOE)

- Analog drive at 8x 100Gbps PAM4

- Protocol agnostic (Ethernet, PCIe, ...)

- Low latency ~400psec latency

- Low power consumption ~5pJ/bit

### • Architecture

- Optical & electronic monolithic integration

- Ring Resonator modulators at 100Gbps PAM4

- Supports On-Die Laser and External Laser Source

- Fostered an industry eco-system for co-packaging of silicon PICs

- OE fiber attachment with optical connectors

- OE electrical socket

- OE assembly and test

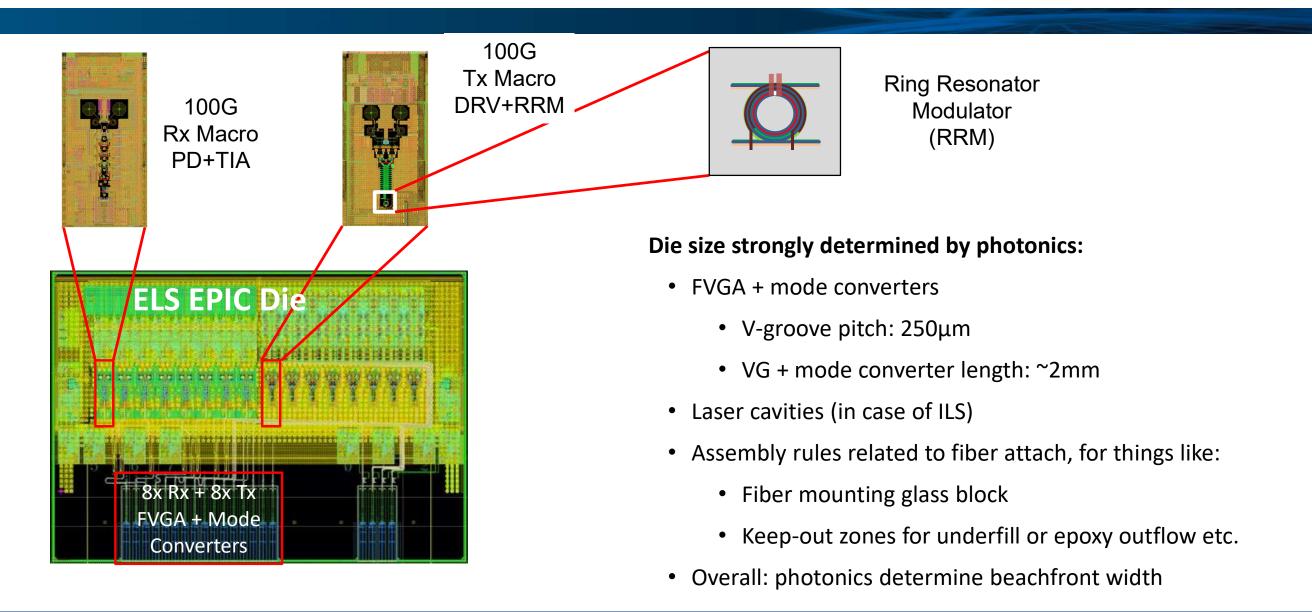

## Odin<sup>™</sup>8P EPIC, ILS Version – Key Functional Blocks

## RANOVUS

## Ring Resonator Modulator (RRM) Design

# RANOVUS

### System Simulation input: Proprietary Dynamic Nonlinear RRM Time Domain Model

14 September 2022

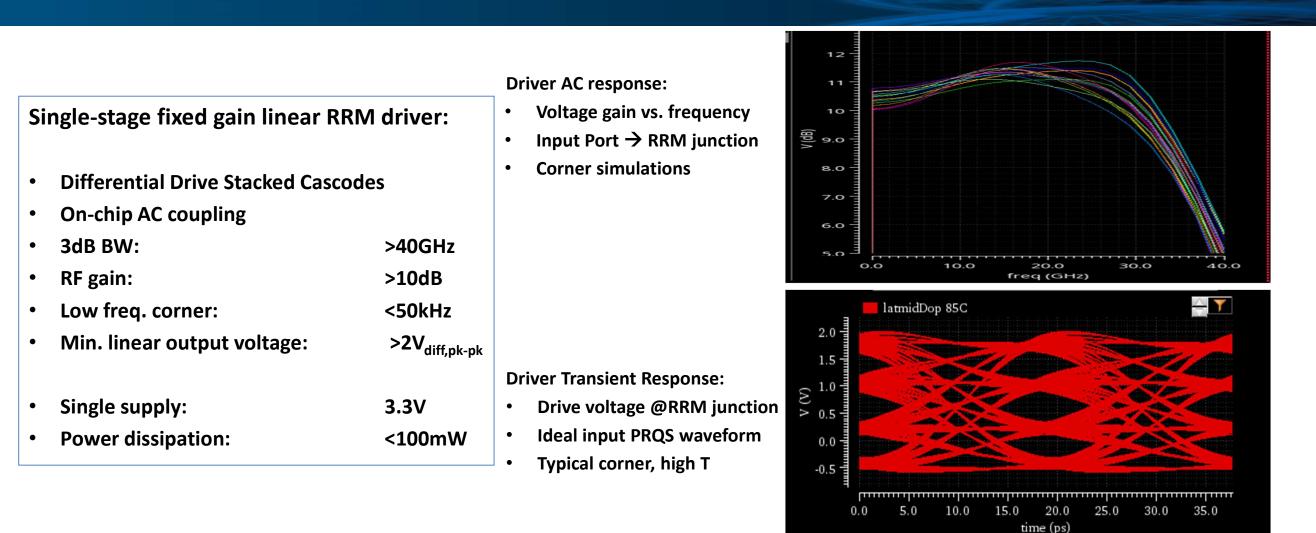

## 100G Tx Macro (DRV+RRM)

### Design Requirements & Extracted Simulation, Samples

### System simulation input: time domain waveforms or frequency responses

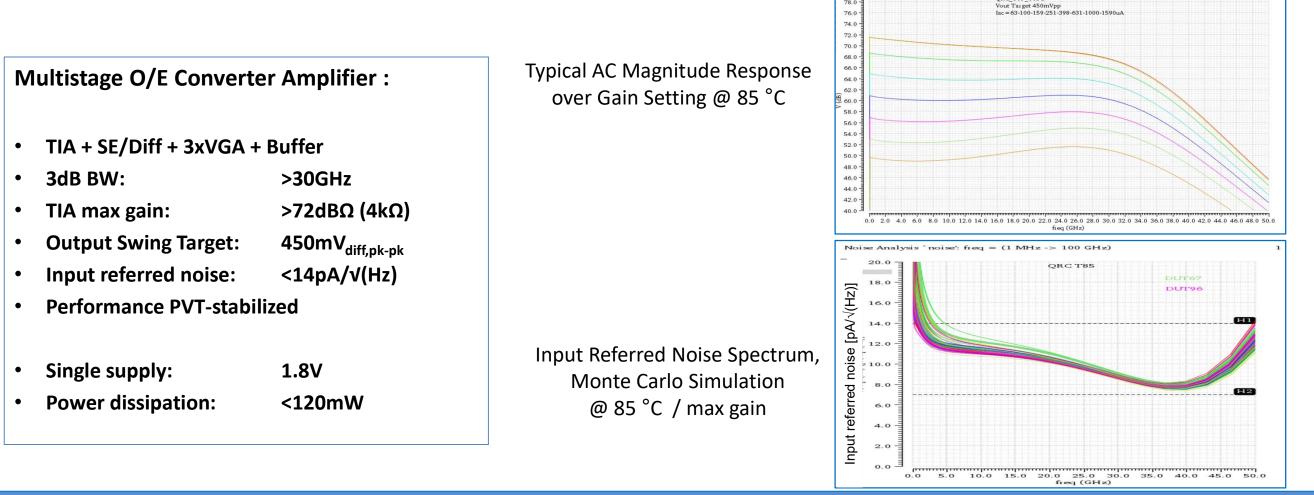

## 100G Rx Macro (PD+TIA)

### Design Requirements & Extracted Simulation, Samples

ORC TYP T850

78.0

System simulation input: time domain waveforms or frequency responses (e.g. magnitude, phase + noise spectral density)

14 September 2022

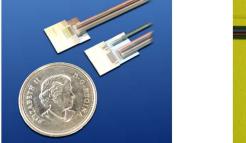

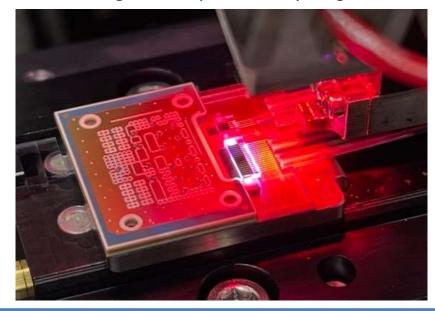

## ODIN<sup>™</sup> EPIC Fiber Attach & Packaging

# RANOVUS

16 Fiber passive V-Groove attach system

- Flip-chip technology used for SiP with V-Groove

- Passive attach of 16 fiber array

- Performance Targets: Insertion Loss <2dB per facet/connection across complete 16 channel fiber array

- Reliability: Telcordia Damp Heat, High-Temperature Storage & Temperature Cycling

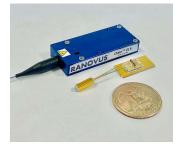

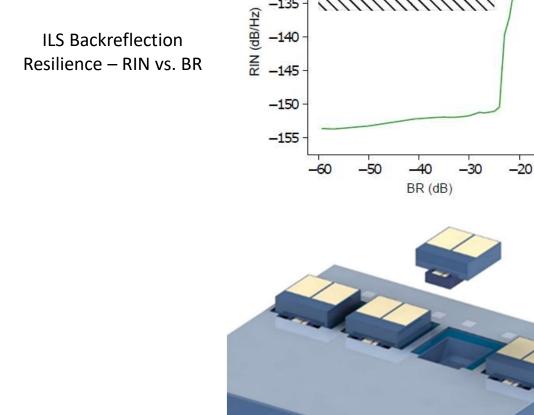

## **O-Band Lasers for EPIC Integration**

### ILS concept

- Odin<sup>™</sup> DFB O-Band Laser

- **Co-Designed to support SiP Optical/Physical Interface**

- Optical

- Designed for backreflection (BR) resilience

- Isolator free interface

- RIN (Relative Intensity Noise) performance under BR

- Power/Size Efficiency

- Physical

- Size minimized for EPIC mounting

- Customized for precise passive mounting

- Innovative laser mounting mechanism, supporting

- Mounted/soldered laser and test before attach

- Relaxed tolerances for submount attach

- Burn in capability before attach

- Features and facility to perform machine vision/optical alignment

-125

-130

-135

**ILS Backreflection**

# RANOVUS

### What did we demonstrate at OFC?

## RANOVUS

### Demonstrated error free Ethernet links for $100G/\lambda$

14 September 2022

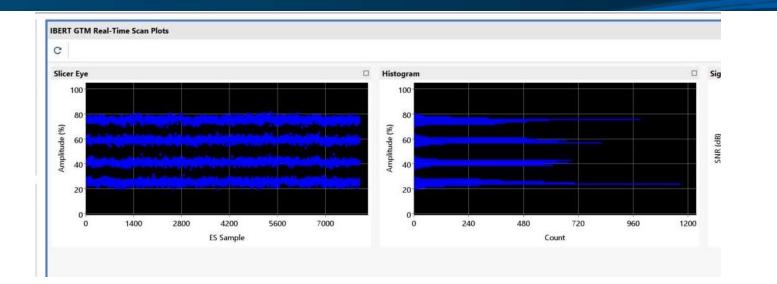

## 106.25Gbps PAM4 Fiber Loopback BER

#### 100G PAM4 - Slicer Eye & Histogram Sample

| Link Group 0 (8) |                                                   | Reset | Reset | Reset |              |          |         | BER      | PRBS 31 | v | PRBS 31 |

|------------------|---------------------------------------------------|-------|-------|-------|--------------|----------|---------|----------|---------|---|---------|

| 🗞 Link 0         | IBERT_0.Quad_206.CH_2.TX IBERT_0.Quad_206.CH_2.RX | Reset | Reset | Reset | 106.219 Gbps | 4.359E12 | 5.773E5 | 1.275E-7 | PRBS 31 | ~ | PRBS 31 |

| 🗞 Link 1         | IBERT_0.Quad_206.CH_0.TX IBERT_0.Quad_206.CH_0.RX | Reset | Reset | Reset | 106.219 Gbps | 4.301E12 | 5.68E4  | 1.283E-8 | PRBS 31 | ~ | PRBS 31 |

| & Link 2         | IBERT_0.Quad_205.CH_2.TX IBERT_0.Quad_205.CH_2.RX | Reset | Reset | Reset | 106.242 Gbps | 4.273E12 | 2.497E5 | 5.753E-8 | PRBS 31 | ~ | PRBS 31 |

| 🗞 Link 3         | IBERT_0.Quad_205.CH_0.TX IBERT_0.Quad_205.CH_0.RX | Reset | Reset | Reset | 106.219 Gbps | 4.125E12 | 1.272E4 | 3.004E-9 | PRBS 31 | ~ | PRBS 31 |

| 🗞 Link 4         | IBERT_0.Quad_204.CH_2.TX IBERT_0.Quad_204.CH_2.RX | Reset | Reset | Reset | 106.219 Gbps | 4.02E12  | 2.301E5 | 5.731E-8 | PRBS 31 | ~ | PRBS 31 |

| 🗞 Link 5         | IBERT_0.Quad_204.CH_0.TX IBERT_0.Quad_204.CH_0.RX | Reset | Reset | Reset | 106.219 Gbps | 3.922E12 | 2.73E4  | 6.847E-9 | PRBS 31 | ~ | PRBS 31 |

| 🗞 Link 6         | IBERT_0.Quad_203.CH_2.TX IBERT_0.Quad_203.CH_2.RX | Reset | Reset | Reset | 106.219 Gbps | 3.686E12 | 1.153E5 | 3.073E-8 | PRBS 31 | ~ | PRBS 31 |

| & Link 7         | IBERT_0.Quad_203.CH_0.TX IBERT_0.Quad_203.CH_0.RX | Reset | Reset | Reset | 106.242 Gbps | 3.688E12 | 6.131E4 | 1.669E-8 | PRBS 31 | ~ | PRBS 31 |

#### 100G PAM4 8 channels BER results

### BER in the range of 3E-9 to 1E-7 (>3 decades of margin vs. IEEE spec)

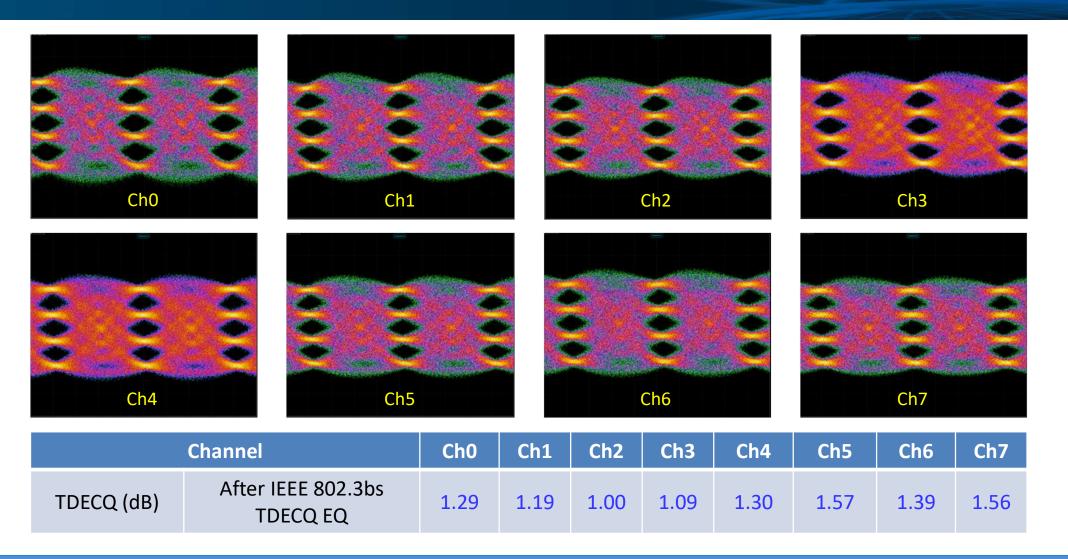

### **106.25Gbps PAM4 TX Quality** Averaged Optical Tx from ODIN<sup>™</sup>8P

### **Optical Tx passing IEEE 802.3bs TDECQ spec (< 3.5dB) with good margin**

14 September 2022

# RANOVUS

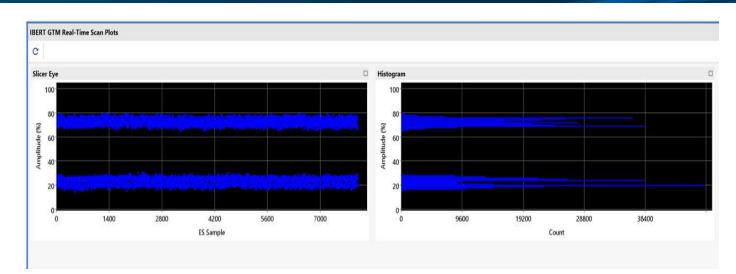

## 32Gbps NRZ Fiber Loopback BER

#### 32G NRZ – Slicer Eye & Histogram Sample

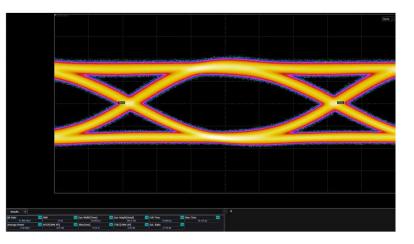

32G NRZ Eye Diagram Sample @Rx Output

### **ODIN<sup>™</sup>** is protocol & data rate agnostic – ready to support PCIe Gen5 application

Thank You!

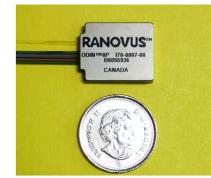

## **RANOVUS Odin**<sup>™</sup>

Multi Terabit platform for optical interconnect