## HOLISTIC TRANSFORMATION IN HIGH VOLUME MANUFACTURING OF DATA CENTER TRANSCEIVERS

Tolga Tekin

Photonic & Plasmonic Systems Fraunhofer Institute for Reliability and Microintegration (IZM), Berlin

#### Acknowledgement

MASSTART project is co-funded by the Horizon 2020 Framework Programme of the European Union with Grant Agreement Nr. 825109. <u>https://cordis.europa.eu/project/rcn/219912/factsheet/en</u>

MASSTART project is an initiative of the **Photonics Public Private Partnership**. <u>www.photonics21.org</u>

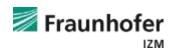

## Empowering Photonic Interconnects for Data Center and Next Generation Computing

#### Fraunhofer IZM:

- System concept and design

- Photonic and RF component design

- Signal integrity and board design

- Silicon photonics interposer

- Through silicon via (TSV)

- 3D integration

- Flip chip assembly

- Co-packaging

- System evaluation

- Benchmarking

## **Empowering Photonic Interconnects**

for Data Center, Next Generation Computing, Next Generation Networks

#### PROMETHEUS

Programmable photonics enabling ultra-fast spiking and quantum neural networks

#### OCTAPUS

Optical circuit switched time sensitive network architecture for high-speed passive optical networks and next generation ultra-dynamic and reconfigurable central office environments

#### ADOPTION

Advance co-packaged optics enabling high-efficiency cloud computing

#### ALLEGRO

Agile ultra low energy secure networks

Tolga Tekin, PPS 3 EPIC, 07.09.2022 © Fraunhofer IZM

2

3

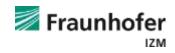

## **Data Center Architecture Metrics**

Also interface to metro network

•

Tolga Tekin, PPS 4 EPIC, 07.09.2022 © Fraunhofer IZM

Tier 2 switches service a "Co-location"

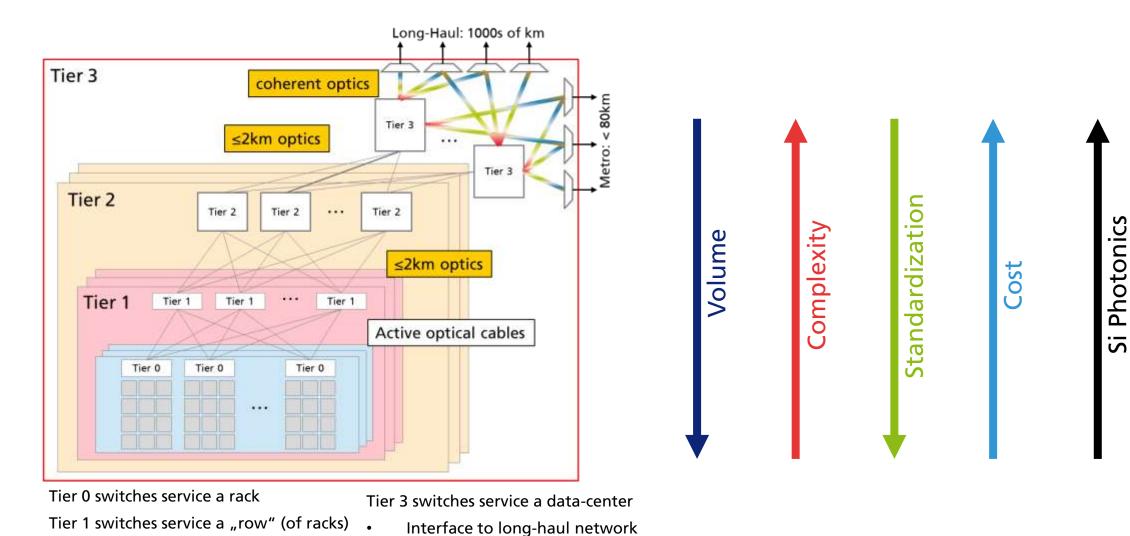

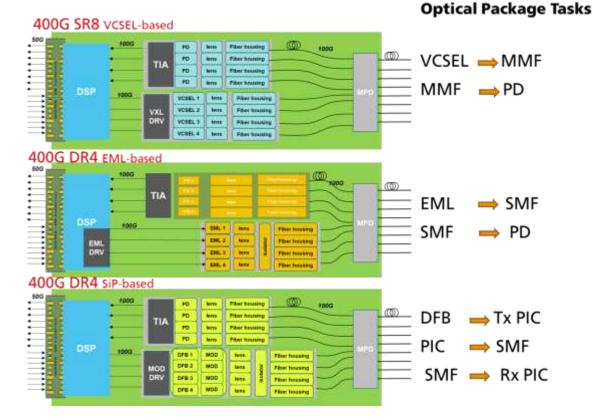

## **Data Center Transceiver Metrics**

#### **Higher Reliability**

*Transceiver failures in the DC requires constant maintenance*

Tolga Tekin, PPS 5 EPIC, 07.09.2022 © Fraunhofer IZM

## **Cost, Power and Reliability Optimization Requirements**

Innovation in Optical

Packaging

- Design for high volume manufacturing: passive or fully-automated

- Design for reduced BOM

- Eliminate labor-intensive alignment steps (COGS)

- Support extended reach, high temperature with single design

- Support all data rates with a single optical design

Tolga Tekin, PPS © Fraunhofer IZM

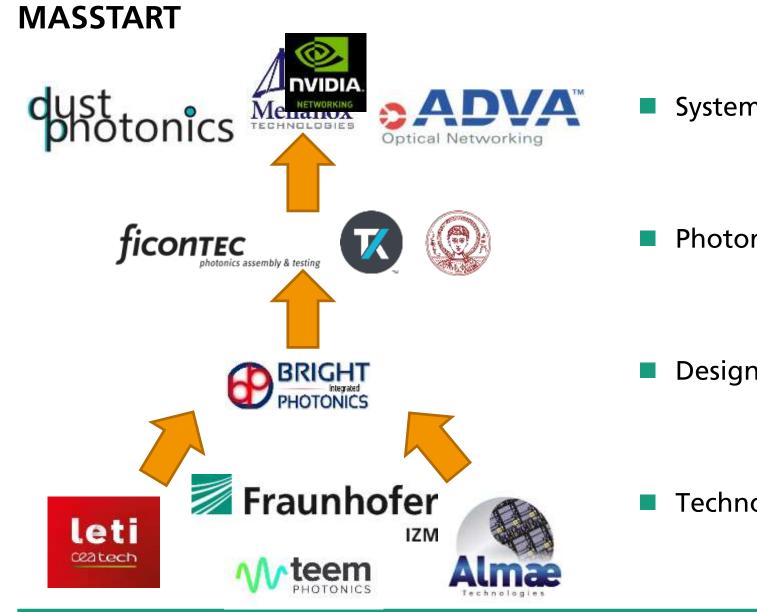

Design House & Technology consultancy

Technology providers

Tolga Tekin, PPS 7 EPIC, 07.09.2022 © Fraunhofer IZM

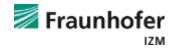

# High-Power DFB Lasers based on Almae WAFT : Pitch and Mode Adaptation Al-free MQW

- Uncooled DFB with low Ith and high Pout

- Compatible with SiBH technology

## New generation of HPDFB

The output power is improved by 25% at high temperature operation

Tolga Tekin, PPS 8 EPIC, 07.09.2022 © Fraunhofer IZM

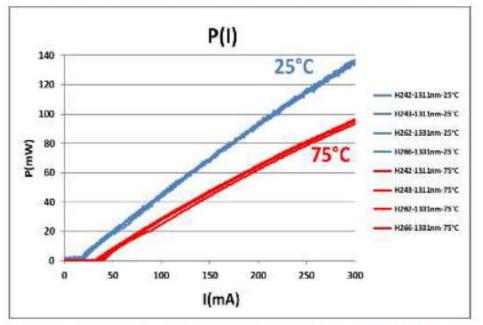

- Insertion loss (incl. fiber) <0.7dB</p>

- MFD 4x3µm (1/e2), pitch >20µm

- SM and PM compatible

#### MFD matching to PIC edge couplers

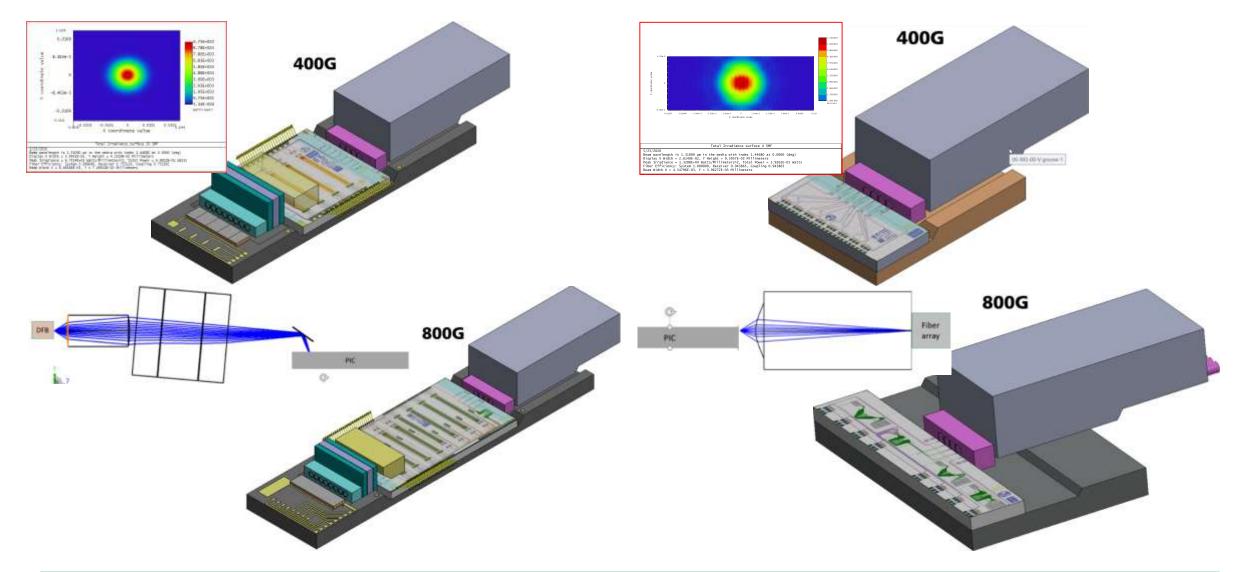

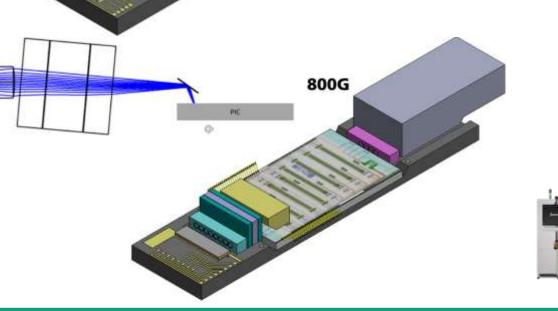

## Inter- and Intra- Data Center Design Challenges up to 1.6 Tb/s

- Multiple technologies: Si-Photonics, III-V, Glass

- PDK for separate technology mapped layers

- Multiple IP Building Blocks

- Complex routing and design rules

- New generation of assembly, coupling and packaging approach

- Create packaging rules, packaging templates, import fiducial markers

BRIGHT

Tolga Tekin, PPS 9 EPIC, 07.09.2022 © Fraunhofer IZM

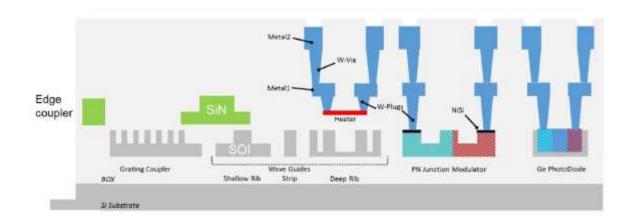

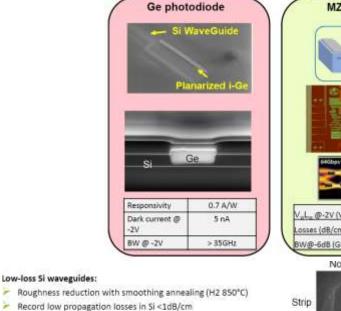

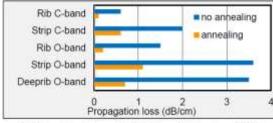

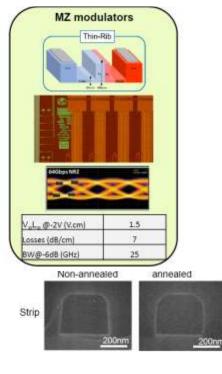

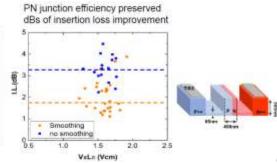

## Silicon Photonics Technology KPIs and Device Libraries

- Advanced 300mm Si platform

- Substrates : SOI 310nm and 220nm

- Si patterning with immersion lithography

- 60nm smallest feature size

- > 200 steps ; 24 litho levels

- 40 metro/control steps

- Low optical losses: 0.6-2 dB/cm

- Versatility: combine building blocks

- No shape modification: no impact on other devices

- No impact on modulator efficiency

| Strip WG @1310nm | 1.1dB/cm |

|------------------|----------|

| Strip WG @1550nm | 0.7dB/cm |

Q. Wilmart et al., Journal of Lightwave Technology (2021)

leti

Ceatech

Tolga Tekin, PPS 10 EPIC, 07.09.2022 © Fraunhofer IZM

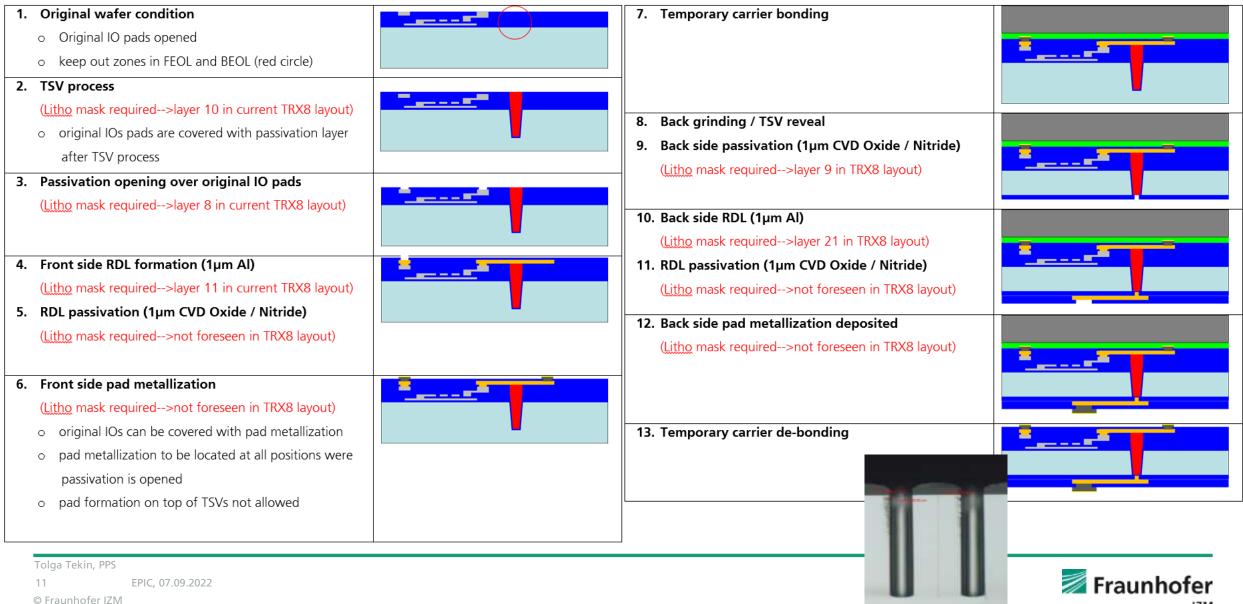

## Front and Back Side Processes for TSV, RDL and IO formation

IZM

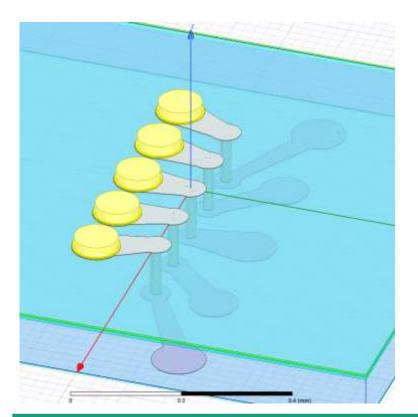

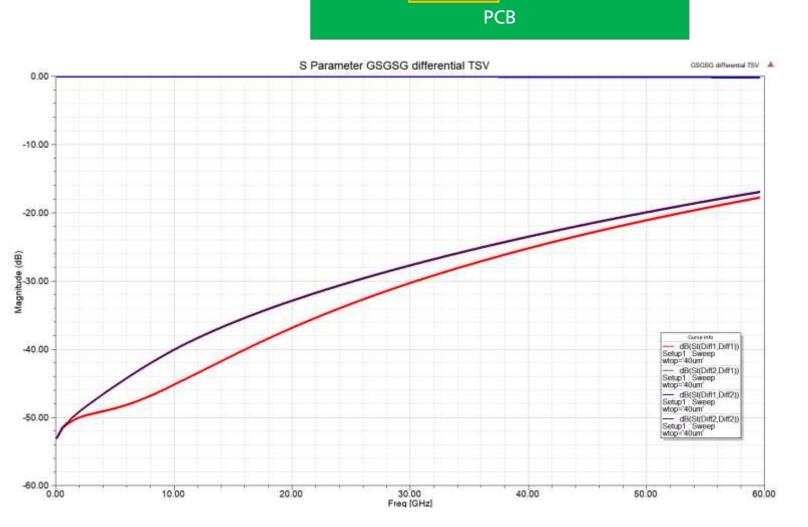

## **GSGSG TSV Application Scenario / Co-Packaging**

Required to connect:

- Driver/TIA chips assembled on top of the Interposer

- DSP chip assembled on the PCB

DSP

TIA/DRV

Si Interposer

Tolga Tekin, PPS 12 EPIC, 07.09.2022 © Fraunhofer IZM

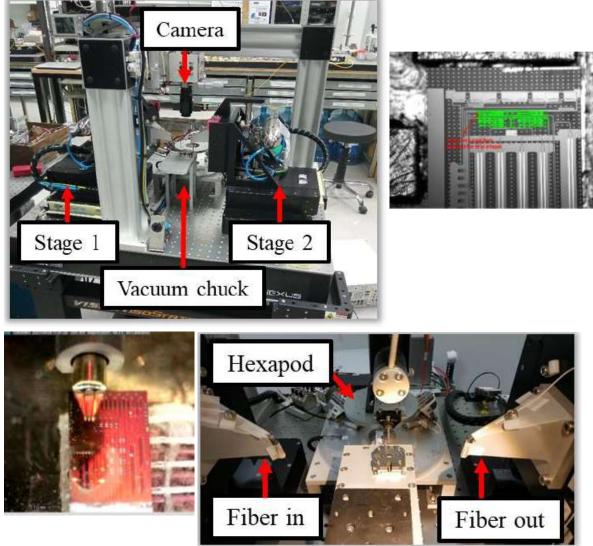

## **Module Coupling**

805-00

ALC: NO 810-03 100-01 805-005 16-001 400G

0.000

1.019

-1.400

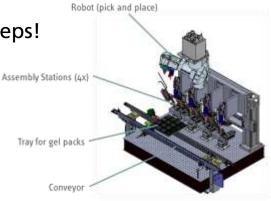

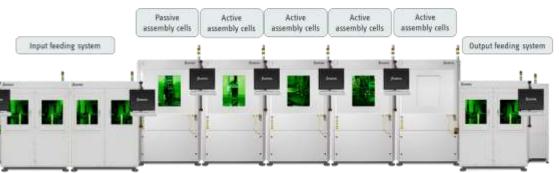

### ficontec **Mass manufacturing line** for DC interconnects (possible layout)

- Final cost defined by

- Machine costs

- Footprint / Clean room area

- Throughput of all assembly steps!

🜌 Fraunhofer

Tolga Tekin, PPS 13 EPIC, 07.09.2022 © Fraunhofer IZM

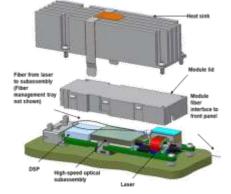

# Coherent transceiver with 600Gb/s capacity (DP-64QAM)

- A tunable single-wavelength

- Following the DP-64QAM modulation format on 64Gbaud/s line rate

- Engine for pluggables and line-cards

- Modulator, receiver, driver, TIA and control IC

- Solder reflow compatible

- BGA contacts for highest RF-performance

- OIF standard, 15 x 22.5 x 3.6mm footprint

Source: ADVA

## 4-Channel PSM4 Module in QSFP-DD Format with 400G Aggregate Bit Rate

**Rosenberger Based Prototype**

Ardent Based Prototype

Tolga Tekin, PPS 14 EPIC, 07.09.2022 © Fraunhofer IZM

## How to enable mass-manufacturing of datacom photonics products?

- Automated manufacturing

- Optical transceivers transfer rates > 1Tb/s

- Competitive costs according to the interconnection distance

- Proven designs

- Chip manufacturing (photonic/electronic)

- Integration & Packaging

- Testing

- Demonstration in a real environment

- Standardization

- PIC-based optical transceivers with transfer rates above 1Tb/s enabling massive deployment in datacenter environments (<1€/Gbps between racks and <0.1€/Gbps inside racks)</p>

### → Ecosystem and improved cross fertilization between photonics and other technology areas

#### 8th International Symposium for Optical Interconnect in Data Centres

Wed., 21. September 2022,

ECOC 2022, Basel, Switzerland

### MASSTART Project

19.-21. September 2022,

Berlin-Brandenburg Pavilion (booth #411) ECOC Exhibition 2022, Basel, Switzerland

#### Applause ECSEL Project

#### Heterogenous Integration Summer School

29.-30. September 2022,

ESREF 2022, Berlin, Germany

#### We are constantly looking for new talents!

**Optical** - wireless networks

Photonic neural networks

Tolga Tekin, PPS 16 EPIC, 07.09.2022 © Fraunhofer IZM

## **Transmit and Receive Module Coupling**