The views, opinions and/or findings expressed are those of the author and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government

#### Photonic Integration and Pathfinding with Intel FPGAs

Mr. Conor O'Keeffe Principal Engineer

CTO Group Programmable Solutions Group Intel

#### Intel

Date: 7<sup>th</sup> September 2022

# Agenda (20mins + 10min)

- Some DARPA Program Examples

- Figures of Merit

- DARPA CHIPS and the Era of Chiplets

- DARPA PIPES Heralding Fiber from Compute Package

- DARPA Space-BACN and Coherent Free-Space-Optics for LEO Satellite Constellations

- Future Research Initiatives

- Conclusion

- Q&A

# Intel's participation on some of DARPA Photonic Integration Programs

- CHIPS Common Heterogeneous Integration and IP Reuse Strategies

- Standardized Interfaces for Interoperable Chiplets for 'System in Package'

- Integration demonstration of Highspeed Data-converters and Photonic Transceivers

- FoM sets following metrics << 1pJ/bit and > 220Gbs/mm Shoreline

- 'System in Package' Development Cost and Schedule reduced compared to Monolithic Designs

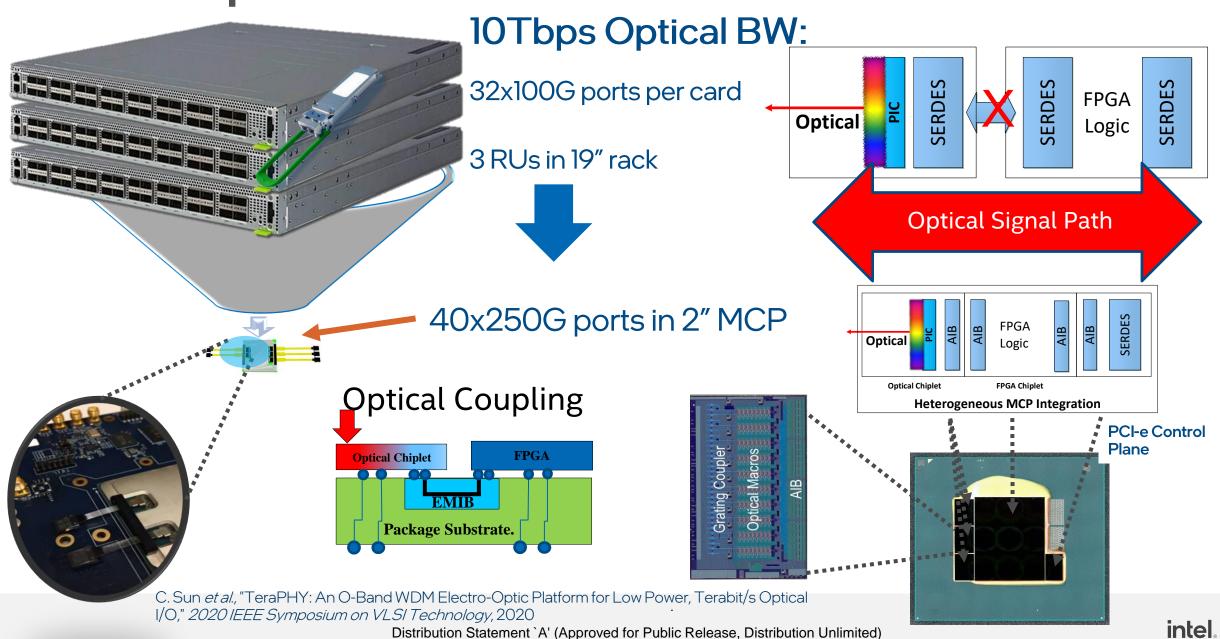

- PIPES Photonics In the Package for Extreme Scalability

- Aim of 100Tbs @ <1pJ/b >1km per Package (Phase 3)

- Phase 1, 2.5pJ/b 1Tbs/mm 10Tbs/Package

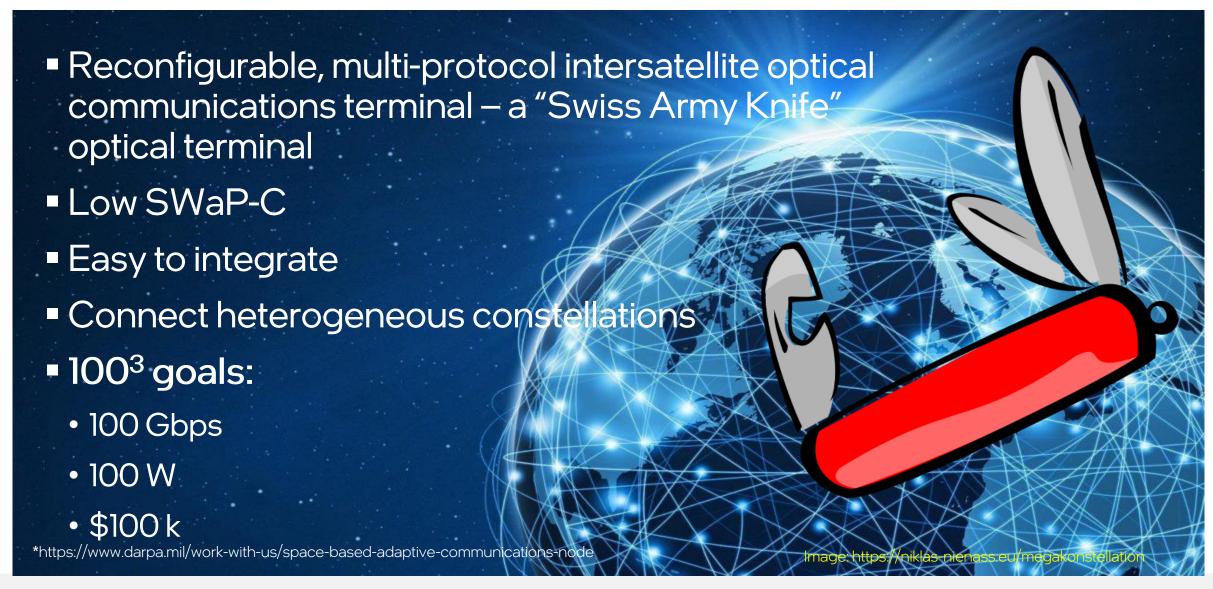

- Space-BACN Space-Based Adaptive Communications Node

- Coherent Multi-waveform/FEC/Protocol Modem

- 100<sup>3</sup> \$100K, 100W, 100Gbs

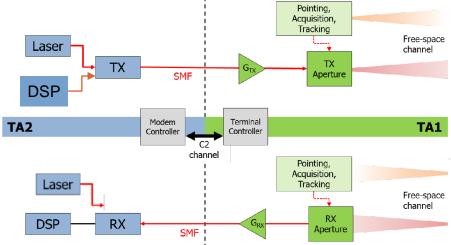

- 3 Technical Areas, Optical Head (TA1), Optical modem (TA2) and Constellation Control (TA3)

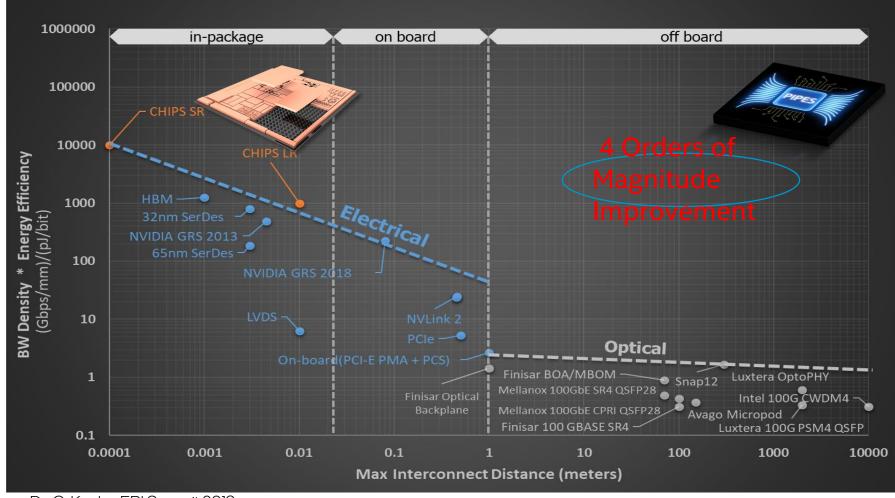

#### Two Interconnect Bottlenecks

Dr. G. Keeler, ERI Summit 2019

- 1. Solve Chiplet Integration Bottleneck (CHIPS) intra-package

- 2. Solve Optical Bandwidth Power and Density through Optical Integration (PIPES)

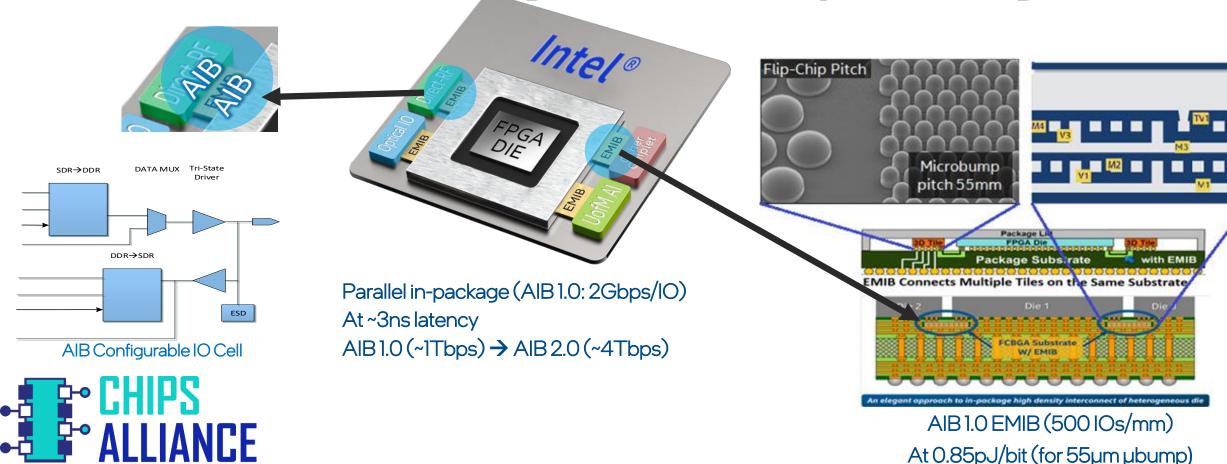

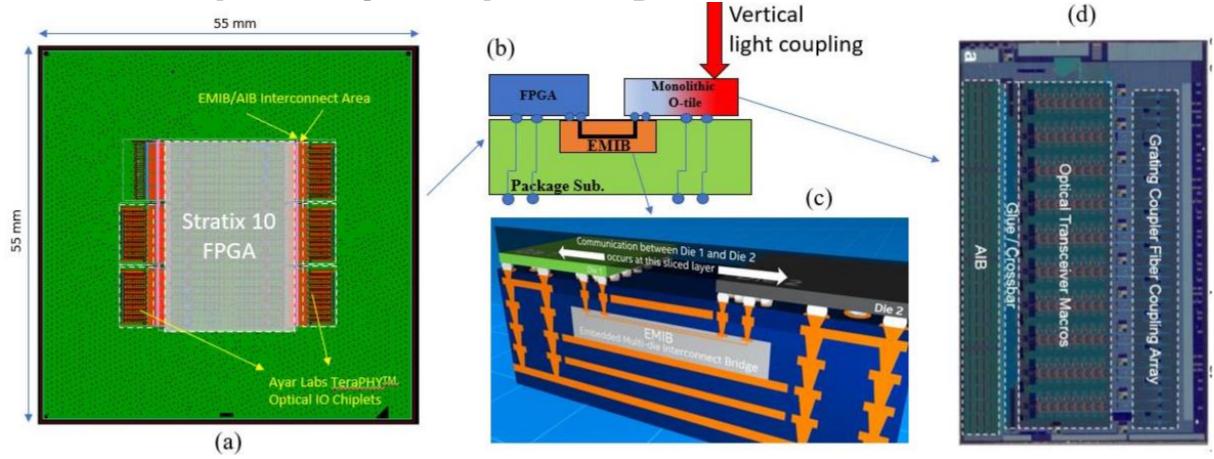

Intel EMIB for Heterogeneous Chiplet Integration

Standardization through CHIPS Alliance and UCle AIB 1.0 and AIB2.0 Open-Source Specifications

https://github.com/intel/aib-phy-hardware

https://github.com/chipsalliance/AIB-specification/blob/master/AIB Specification%202 0.pdf

AIB: Advanced Interface Bus UCIe: Universal Chiplet Interconnect Express IO: Input/Output

#### DARPA CHIPS

"It may prove to be more economical to build large systems out of smaller functions, which Gordon E. Moore are separately packaged and interconnected."

(1965)

Mahajan, R., et al, "Embedded Multi-Die Interconnect Bridge (EMIB) – A High Density, High Bandwidth Packaging Interconnect," presentation at IEEE 66<sup>th</sup> Electronic Components and Technology Conference, May 2016.

#### Phase 1 Package design included Chiplets

- 2 X Quad ADC/DAC 64 GSps Jariet Technologies (GF11)

- 2 X TeraPHY 2.56 Tbs WDM Chiplet Ayar Labs (GF45)

- 1 X SERDES Chiplet Intel (TSMC 16)

- 1 X A.I. Accelerator Chiplet, University of Michigan (Intel 16)

- 1 x Intel Stratix 10 FPGA (Intel 14)

- 6 x EMIB (Intel)

Several other MCP developments in the program expanding the Ecosystem of interoperable Chiplets

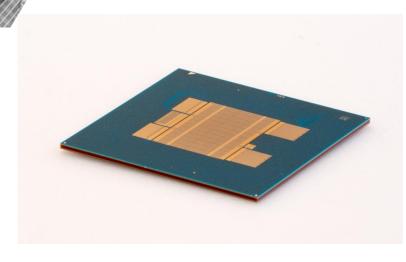

## PIPES Optical Module

8Tbs Optically Co-packaged FPGA

K. Hosseini, E. Kok, S. Y. Shumarayev, C. Chiu, A. Sarkar, A. Toda, Y. Ke, A. Chan, D. Jeong, M. Zhang, S. Raman, T. Tran, K. A. Singh, P. Bhargava, C. Zhang, H. Lu, R. Mahajan, X. Li, N. Deshpande, C. O'Keeffe, U. Krishnamoorthy, C. Sun, R. Meade, V. Stojanovic, and M. Wade, "8 Tbps Co-Packaged FPGA and Silicon Photonics Optical IO," in Optical Fiber Communication Conference (OFC) 2021,

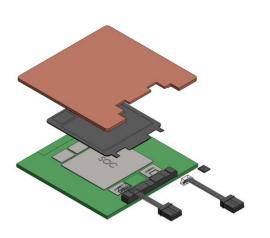

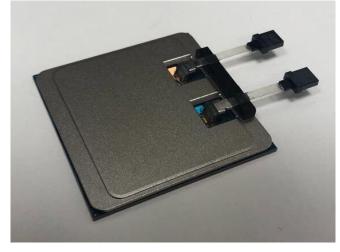

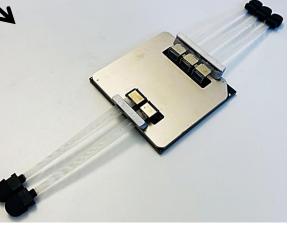

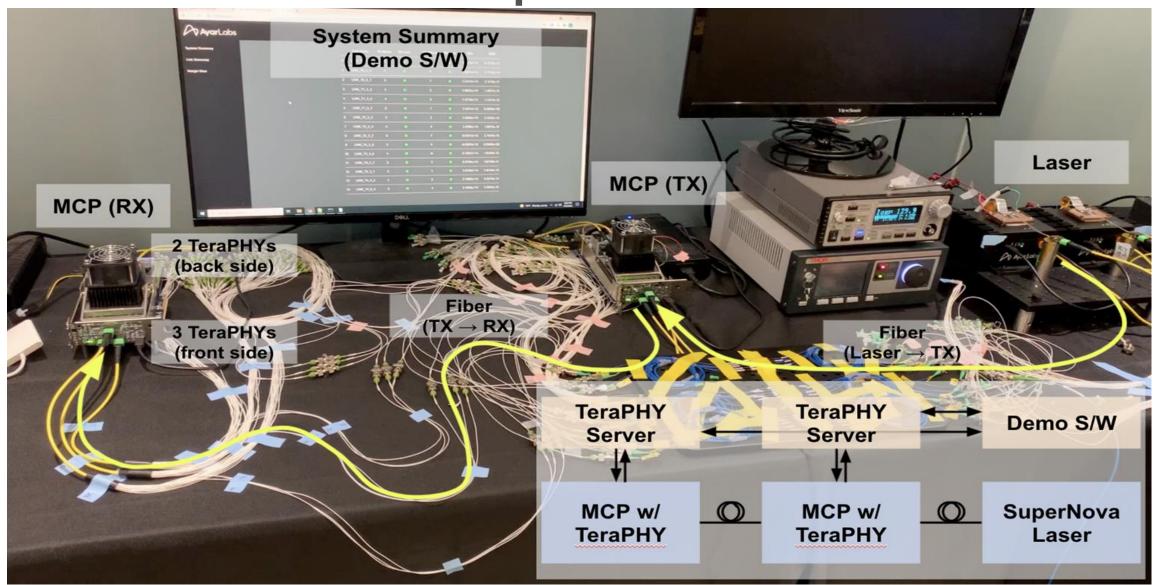

# MCP on Datacenter Type Platform

Intel® FPGA Optical Programmable Accelerator Card (O-PAC) Prototype

PCI-E Form Factor

K. Hosseini *et al.*, "5.12 Tbps Co-Packaged FPGA and Silicon Photonics Interconnect I/O," *2022 IEEE Symposium on VLSI Technology and Circuits* (VLSI Technology and Circuits), 2022, pp. 260-261

# Measurement Set-Up

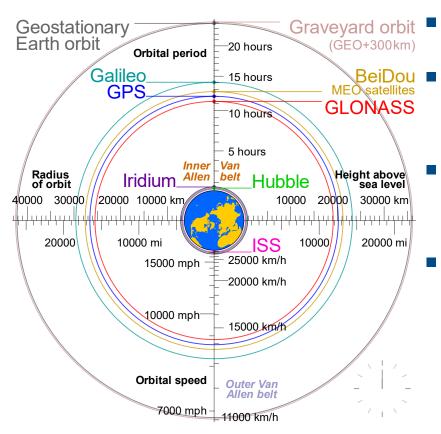

# **LEO Satellite Constellation Compatibility**

- LEO is between 600 km and 2000 km

- Current Operational Satellites: 5465 of which ~4700 are LEO\*

- Worldwide Launches between 2022 and 2030 is >40,000

- OISL Mesh Network Proliferation

- Limited Inter Constellation Compatibility on Protocols, Waveforms, Data rates, Channel

Coding

\* https://www.ucsusa.org/resources/satellite-database

https://en.wikipedia.org/wiki/Low\_Earth\_orbit

LEO: Low Earth Orbit

GPS: Global Positioning System

OISL: Optical Intersatellite Links

# Space-BACN High Level Objectives\*

#### How will it be done?

### 3 Technical Areas

# TA1 Low-cost Coherent Aperture

- •Telescope and Gimbal

- •Fiber connection to TA2

- .EDFA

- Beacon Tracking

#### TA2 Reconfigurable Optical Modem

- •Multi-waveform Support

- .Multi-FEC Support

- Multi-protocol Support

- .Up to 100Gbs

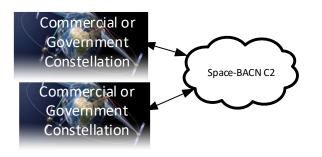

# TA3 Cross-Constellation C2

C2 to manage interaction between Commercial and Government ConstellationsQoS Simulations

Modular Interoperability between different Technical Areas

FEC: Forward Error Correction

# System Requirements

| Program Level Goal           | Reconfigurable Modem                                           | Optical Aperture                          |

|------------------------------|----------------------------------------------------------------|-------------------------------------------|

| Optical Terminal             | Technical Area 2 (TA2)                                         | Technical Area 1 (TA1)                    |

| Link ranges                  | 100 Gbps at 2,500 km, 25 Gbps at 5,000 km, 1 Gbps at 45,000 km |                                           |

| Wavelength range             | Fully tunable/selectable C band laser 1530-1565 nm             |                                           |

| Programmable waveforms       | Reconfigurable modulation                                      | Optical aperture, optical amplifier gain, |

|                              | supporting various single                                      | and noise performance supporting the link |

|                              | wavelength OOK, PPM,                                           | range and data rates                      |

|                              | DPSK, DP-QPSK formats                                          |                                           |

| Power =< 100 W               | =< 40W                                                         | =< 60W                                    |

| Weight <= 10 kg              | =< 2 kg                                                        | =< 8 kg                                   |

| Cost in production =< \$100k | =< \$30k                                                       | =< \$70k                                  |

| 5-Year lifetime in LEO       | Radiation tolerant and                                         | Cross-plane support, radiation tolerant,  |

|                              | cyber-hardened                                                 | and cyber-hardened                        |

| Modularity/Interoperability  | SMF & C2 channel                                               |                                           |

| Pointing, Acquisition and    |                                                                | "Beaconless," in-band-beacon, out of-band |

| Tracking (PAT)               |                                                                | beacon *                                  |

| Support major industry       | Reconfigurable encoding,                                       |                                           |

| standards and                | FEC, framing, open                                             |                                           |

| communication protocols      | standards                                                      |                                           |

Space-BACN Program Solicitation https://sam.gov/opp/e704657b448649a4a5ff7debeb39540a/view

# Leveraging DARPA PIPES and CHIPS for Space-BACN

- Chiplet integration of Photonics, high speed Data-converter/RF technology, DSP and FPGAs

- Phase 1 kicked off July 2022 following a Phase 0 Architecture Phase

# **Further Research Topics**

- Packaging Challenges

- Allowing Compatibility with standard electronic Production Methods Reflow, Pick and Place etc.

- At scale low defect Fiber attach Methods,

- Optical Chip Testing at Probe and Final Test

- Efficient FECs

- Distributed Compute systems leveraging high Bandwidth Low-Latency Interconnect

- Communication Networks with high bandwidth processing Nodes

#### Conclusions

- Chiplets allow for optical co-packaging with High Performance Compute

- High Bandwidth low power Standardized Interconnect enables scaling of Platforms leveraging optical Chiplets as a reusable IP

- More Photonic Integration across Datacenter, Communications, RADAR

- Coherent Free-Space Optics for OISL

#

## **Legal Notices & Disclaimers**

**INTEL CORPORATION LEGAL DISCLAIMER:** This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest forecast, schedule, specifications and roadmaps.

Intel technologies may require enabled hardware, software, or service activation.

No product or component can be absolutely secure.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.