07 September 2022

# Productizing a PIC: from Design IP to Scalable Testing

### About us

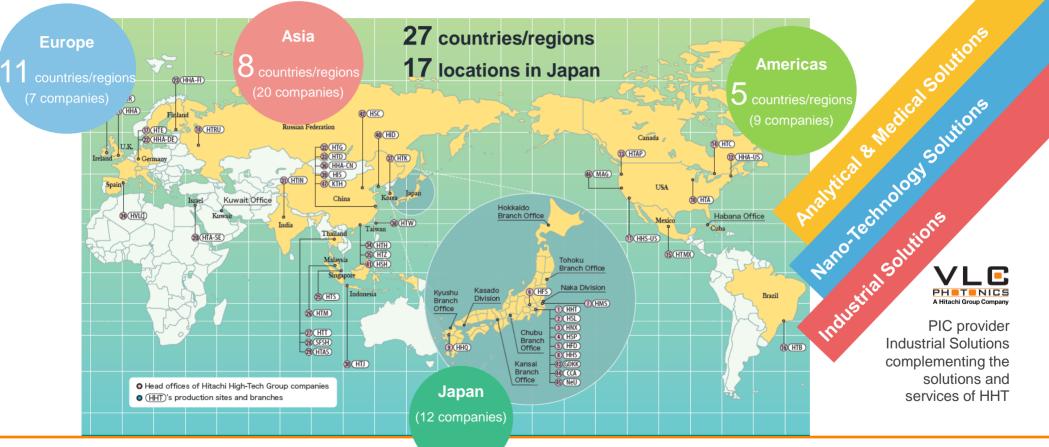

A Hitachi Group Company

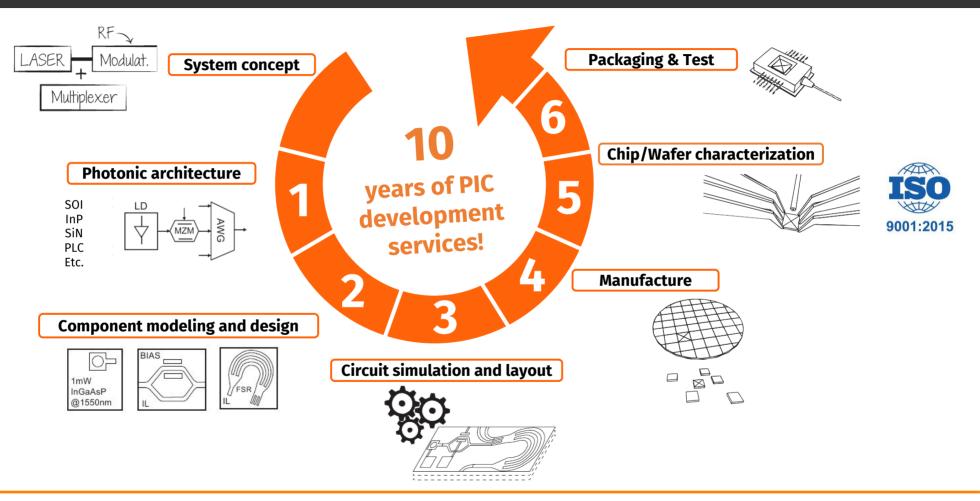

- VLC Photonics offers Photonic Integrated Circuit (PIC) development services, focused on design and testing.

- **C** Company founded in 2011.

- C Offices and clean-room labs in Valencia Technological Campus (Spain).

- 21 members of extensive academic and industrial experience, and keep growing.

- **E** 13+ years in the field of integrated optics and Photonics.

- Part of Hitachi High-Tech group since 2020.

## About us (II)

#### **@Hitachi High-Tech Corporation**

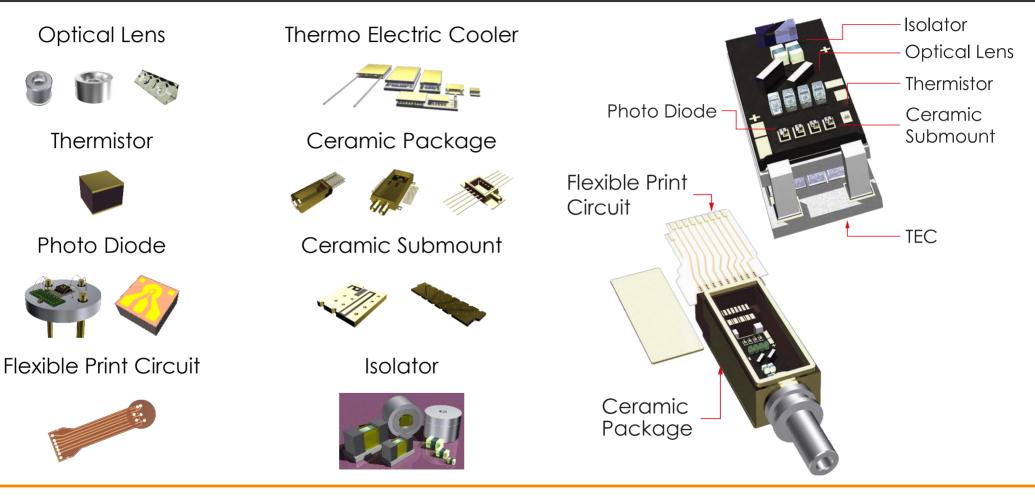

## HHT optical components supply

### Our solutions

## Semiconductor Design IP

- It helps to speed up chip development and lower risk and cost, by licensing validated designs that can be embedded into more complex circuits.

- Semiconductor design IP has been well stablished in the last two decades:

- +3.6B\$ market in 2018

- Fabless companies

- ARM (45%) and Synopsys (17%) dominate market share

- Most of it is digital electronics design

- Main categories are:

- <u>Processor:</u> CPU, DSP and GPU

- <u>Interface:</u> protocol-based function like USB, PCI Express, Ethernet, MIPI, SATA, DP, but also Die-to-Die (D2D) interface and memory controller.

- <u>Other Physical:</u> SRAM and other memory compiler, physical library, Analog & Mixed-Signal, Wireless Interface, etc...

## Differences with photonic design IP

#### • Wafer fabs:

- Electronic foundry landscape dominated by 5 main players: TSMC, UMC, SMIC, Samsung, GF. Well stablished IP ecosystem and framework.

- Photonics foundries are less and smaller. No IP licensing framework.

#### • Cost of design IP validation:

- >250M wafers/year in electronics, very high yields.

- Lot's of R&D, NRE and legal expenses required in photonics compared to the possible market, given the lower TRL.

- Market demand:

- Global electronics market is several orders of magnitude larger than photonics one.

- Most of the photonic product developments are being done by start-ups now.

## Current photonic design IP status

- Most of the players have developed a full fab process, or custom module on top of a generic foundry process.

- Not so fabless anymore, significant CAPEX tied to a fab (~IDM's)

- Differentiation not in design but in front-end/back-end

- Usually offer optical engines = validated PICs

- No open access libraries or PDKs

#### • Lack of standards:

- Many new emerging applications: quantum, LIDAR, AI, AR...

- Design IP is still very customized, limiting its potential customer base

- Risk of development obsolescence in a quickly evolving field

- Lots of interesting patented or published designs by academics or small start-ups lack real-world applicability.

- Validation for a guaranteed commercial offering still very challenging.

- It is still critical to do extensive component / circuit characterization when validating PIC designs towards production.

- Optical alignment

- Opto-electronic measurement

- Processing and Root cause analysis

- When moving to PIC volume production, scalability becomes an issue:

- Functional circuit testing is still required beyond fab metrology and PCM

- Need fast and low cost Wafer/KGD sorting and packaging

- Parallelization is hard, significant CAPEX and setup time required

## Advantages of outsourcing the photonic back-end

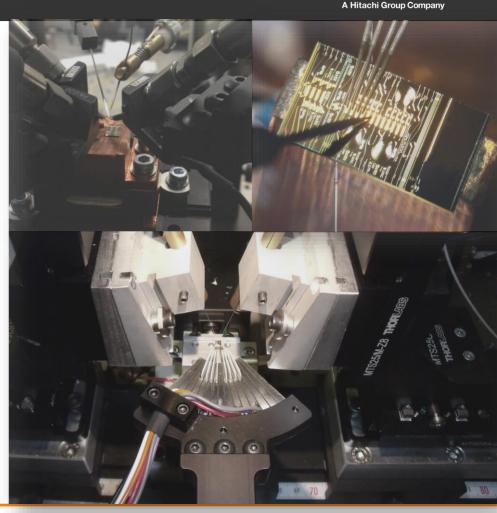

#### **E** Infrastructure investment:

- Cleanroom lab

- Opto-electronic probing stations

- High-end instrumentation

- Consumable stocking

- Redundancy for non-stop operations

#### **E** Engineering expertise:

- Automation

- Photonics

- Big data processing and analysis

- Quality certifications & calibrations

#### E Timing:

- Procurement

- Installation and configuration

- Hiring and training

### Focus on characterization & test

- Close design loop from fabricated to measured devices with big data, allowing for statistical parameter modelling.

- Provide feedback to customers & foundries for process yield improvement, to accelerate product development and volume ramp up.

- Automate identification of KGD to sort dies/wafers in production, and towards packaging.

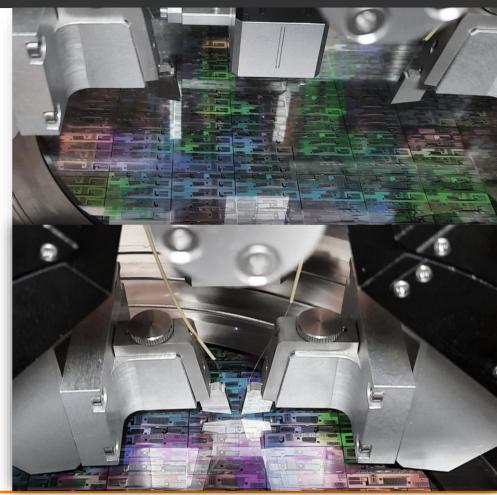

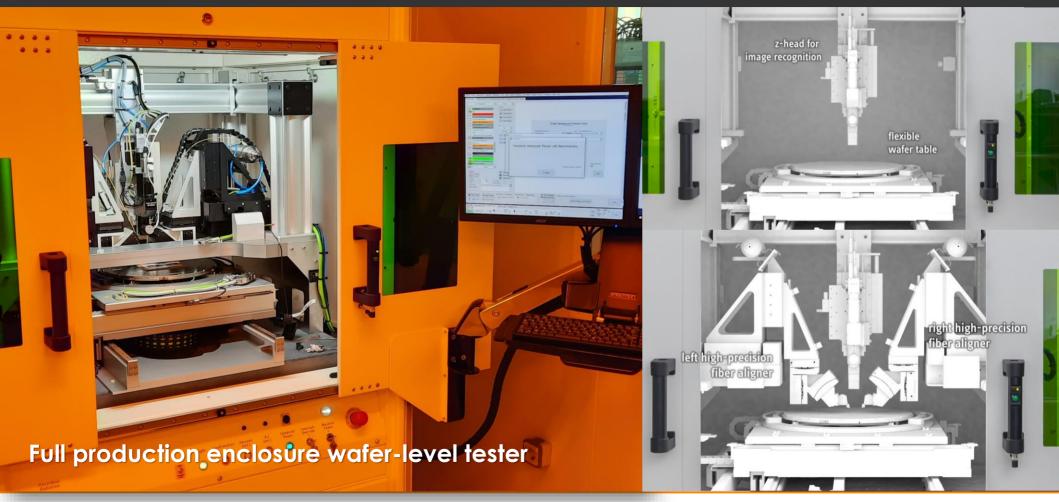

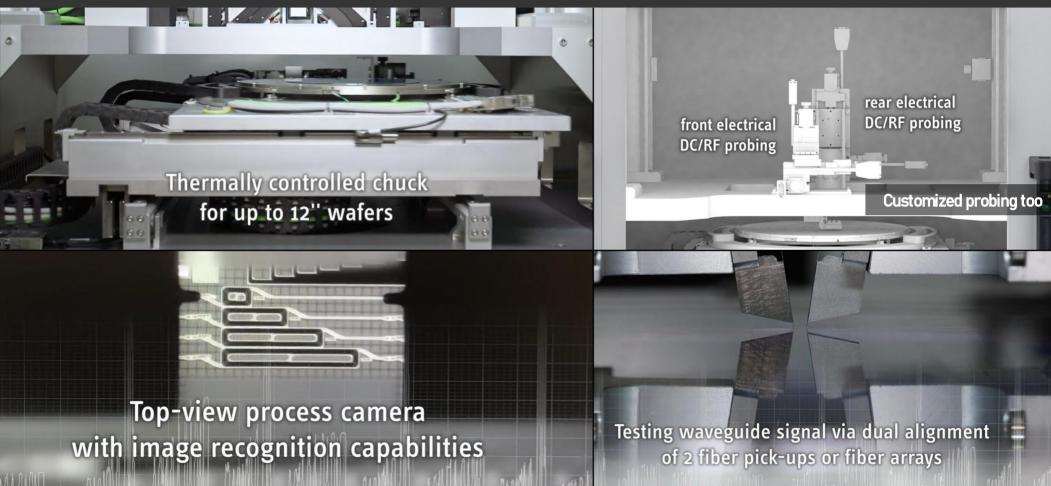

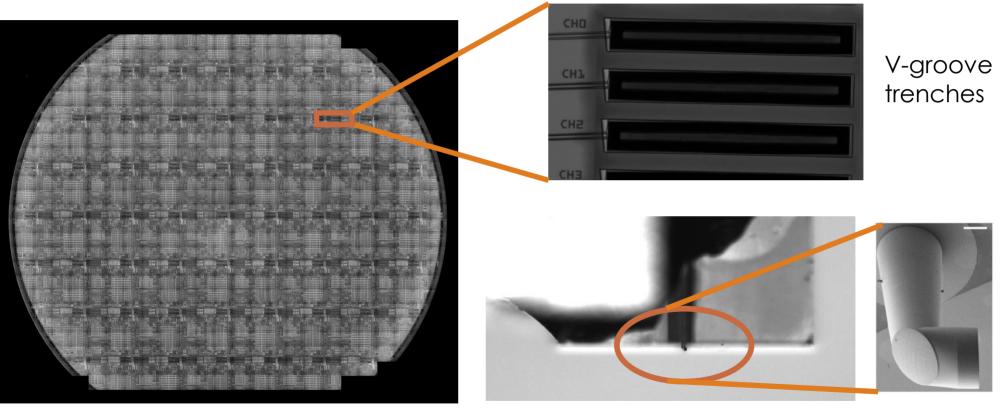

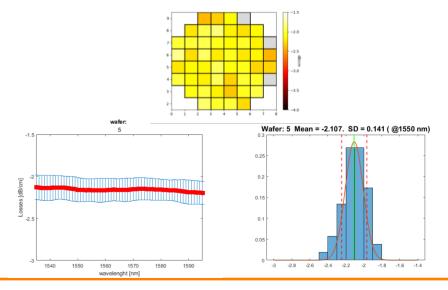

#### Automated Wafer-level Photonic tester

#### **Automated Wafer-level Photonic tester**

### **Automated Wafer-level Photonic tester**

888

<4s optical alignment 0.1/0.4 dB repeatability Depends on fab process and grating coupler design

**Die level testing possible**

## Fully automated data collection and processing

#### Tool and setup scale-up options

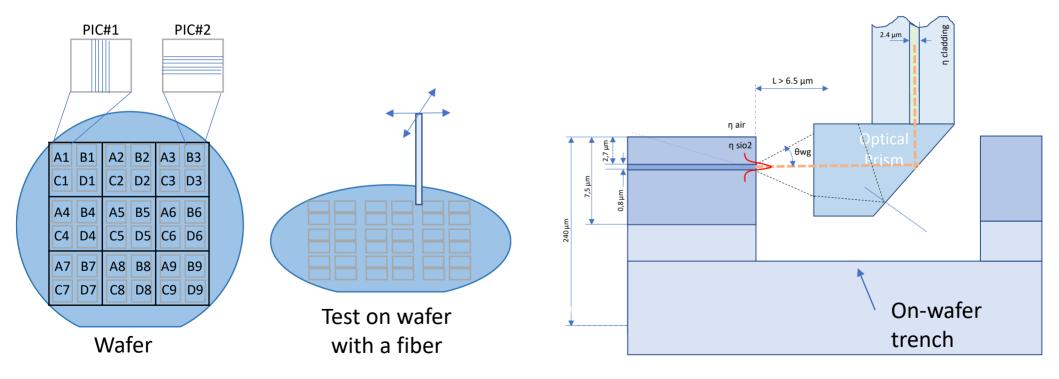

## Edge coupling WLT

#### **C** Tool adapted for optical edge coupling via deep-etch wafer trenches.

## Edge coupling WLT (II)

#### 3D printed micro-lens

MFD 2.3-10.4 µm

## A Hitachi Group Company

#### **Examples of previous projects:**

| DUT                         | Structures | Measurements |

|-----------------------------|------------|--------------|

| Six 6" wafers,<br>>300 dies | >5k        | ~50k         |

| Two 8" wafers<br>>1800 dies | >14.5k     | ~58k         |

| >50 dies                    | >140       | >31k         |

- Fast probing and trace acquisition times are essential when scaling up.

- Smart characterization plan needed for insightful but time-practical test campaign.

#### **Examples of previous projects:**

| DUT                         | Structures | Measurements |

|-----------------------------|------------|--------------|

| Six 6" wafers,<br>>300 dies | >5k        | ~50k         |

| Two 8" wafers<br>>1800 dies | >14.5k     | ~58k         |

| >50 dies                    | >140       | >31k         |

- Fast probing and trace acquisition times are essential when scaling up.

- Smart characterization plan needed for insightful but time-practical test campaign.

- Repeatability of bare die measurements with manual alignment is poor (>0.5 dB).

- WLT ensures that alignment and trace acquisition are done automatically with minimal variations (mechanical, thermal etc.)

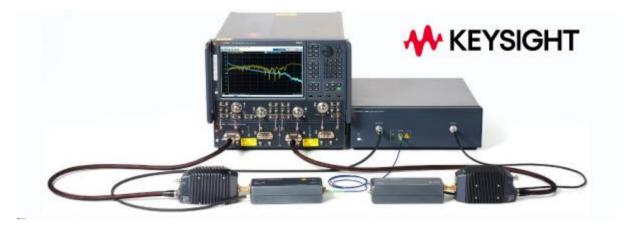

## **RF** testing key for next-gen datacom PICs

- Lightwave Component Analyser (LCA) for parametric testing of devices like high speed modulators in datacom transceivers.

- 110 GHz Turn-Key Test System for Optical RX and TX

- Suitable for die and wafer level testing

- Return to zero and nonreturn-to-zero (RZ / NRZ) and pulse amplitude modulation (PAM) formats

- S-parameter testing over the full 1260 nm to 1620 nm range

- Available for both automated die and wafer level testing

To develop design IP or productize any PIC, characterization and test are significant cost & time bottlenecks.

To produce state-of-the-art PICs in volumen, any photonic back-end technology needs to be scalable from the start.

**3.** VLC/Hitachi High-tech have the resources and expertise to support PIC developments all the way to production.

# Thank you for your attention!

#### **Contact details**

info@vlcphotonics.com

www.vlcphotonics.com

Y

@vlcphotonics

(in)

linkedin.com/company/vlc-photonics