# **Designing Photonic ICs**

#### Pieter Dumon

07/09/2022

EPIC Meeting on CMOS Compatible Integrated Photonics

#### Overview

- OIntro to Luceda and our software

- **O**What we believe in

- OWhere we're going

#### **Luceda Photonics**

### Photonic IC design software

#### Mission:

Help photonic IC designers enjoy the same **first-time** right experience as electronic IC designers

#### **Facts & Figures**

Founded in 2014 as spin-off from imec, Ghent University & VUB

HQ in Dendermonde, Belgium China branch in Shanghai

Growing international team (>20 and hiring)

### **IPKISS Design Platform**

- IC implementation: layout, placement, routing

- GDSII tape-out

- Virtual fabrication

- Device simulation (EM)

- Circuit simulation (behavioral/compact model)

- Netlist extraction and circuit verification

- Standard language: Python

- PDKs for wide range of photonic foundries

#### **Additional modules**

*IPKISS AWG Designer* – synthesis, implementation and simulation of AWG

*IPKISS IP Manager* – regression testing and management of design IP for teams

*IPKISS Link for Ansys Lumerical* – automation of FDTD and MODE simulations

IPKISS Link for Dassault Systèmes Simulia – automation of EM simulations

IPKISS Link for Siemens EDA – link with L-Edit for graphical electrical IC design

### **Photonic IC Design**

#### What we believe in

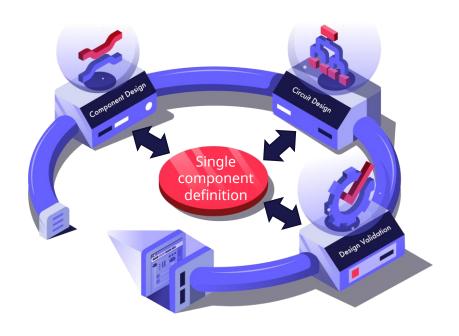

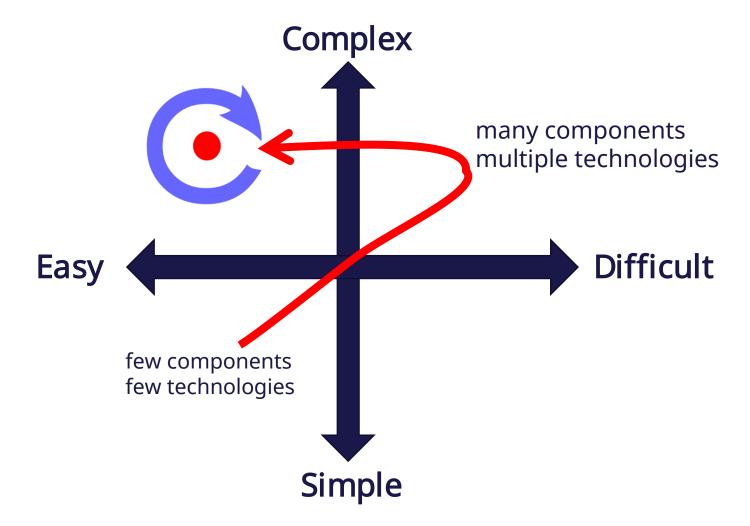

How to make complex photonic IC design easy?

- O Automation Luceda expertise built-in

- O Toolbox empowerment of the designer, flexible and human centric

#### What we believe in

How to make complex photonic IC design easy?

- Use of specification-driven design and HDL correctness and automation

- Direct coupling of specification, layout and simulation avoid mistakes

- High degree of layout automation *productivity* + *avoid mistakes*

- But low-level functions available do what needs to be done

- Manage design IP *persist and control design team knowledge*

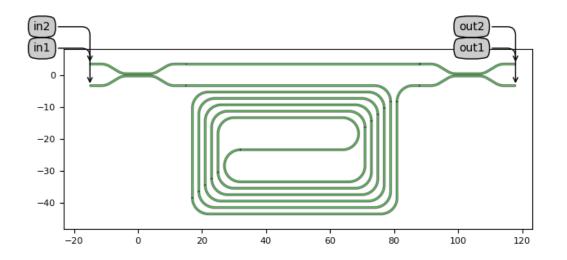

# Specification-driven placement and routing

```

from picazzo3.wg.spirals import FixedLengthSpiralRounded

Built-in components

class MZI(i3.PCell):

class Layout(i3.LayoutView):

def _generate_instances(self, insts):

spiral = FixedLengthSpiralRounded(name=self.name + "_SPIRAL",

trace_template=wg_t, n_o_loops=3, total_length=1000)

spiral_lo = spiral.Layout()

Luceda automates

insts += i3.place and route(

insts={

'splitter': dc,

'combiner': dc,

Placement and routing

'arm1': spiral,

specs

specs=[

i3.Place('splitter', (0, 0)),

i3.Join([

('splitter:out1', 'arm1:in'),

('combiner:in1', 'arm1:out'),

]),

i3.FlipV('arm1'),

i3.ConnectManhattan('splitter:out2', 'combiner:out2'),

External connectivity spec

return insts

def _generate_ports(self, ports):

return i3.expose_ports(self.instances,

{'splitter:in1': 'in1',

'splitter:in2': 'in2',

'combiner:out1': 'out1',

'combiner:out2': 'out2'})

mzi = MZI()

→ Valid and complete layout

mzi_lo = mzi.Layout()

mzi lo.visualize(annotate=True)

```

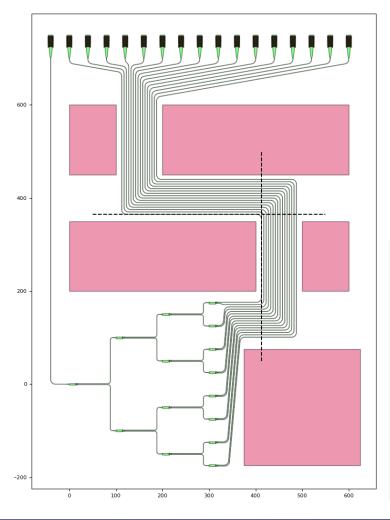

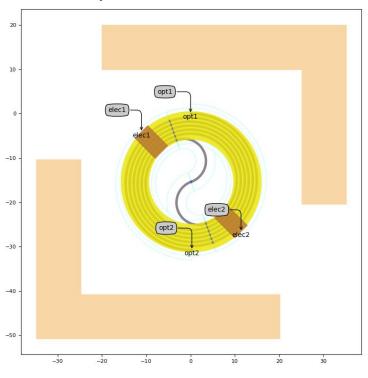

# Specification-driven placement and routing

### Routing

#### Individual routing

```

i3.ConnectBend("gr_out_{}:out".format(cnt), intermediate_port, bend_radius=self.bend_radius),

i3.ConnectManhattan(

intermediate_port.flip_copy(), "DUT:out{}".format(n_gratings - cnt),

bend_radius=self.bend_radius,

min straight=0.0, start straight=0.0,

```

#### Bundle routing

```

bundle = [

i3.ConnectManhattanBundle(

connections=[

('tree:out{}'.format(16 - n), 'gr_out_{}:out'.format(n)) for n in range(16)

start_fanout=i3.SBendFanout(max_sbend_angle=85., reference='tree:out16'),

end fanout=i3.SBendFanout(max sbend angle=80, end position=(150, 600)),

pitch=pitch,

bend_radius=bend_radius,

control_points=[i3.V(412.5), i3.H(365)],

control_point_reference='tree:out16',

```

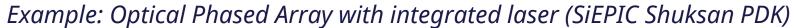

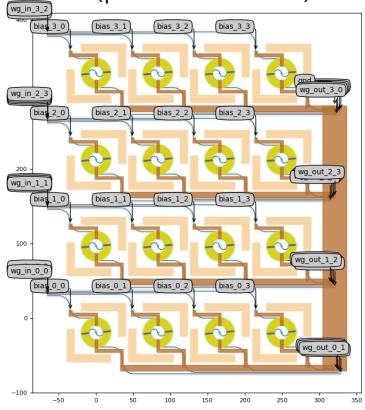

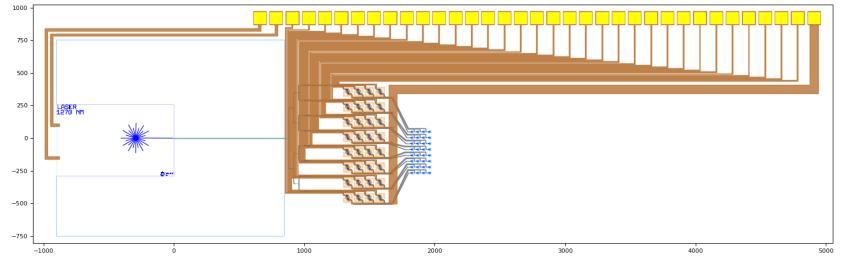

# Hierarchical, parametric design

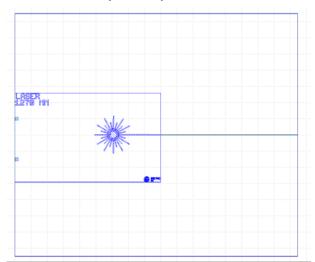

#### Laser (PDK)

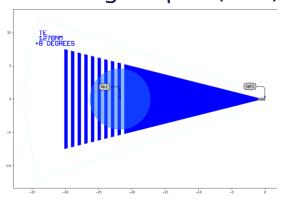

#### Grating coupler (PDK)

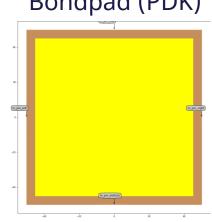

Bondpad (PDK)

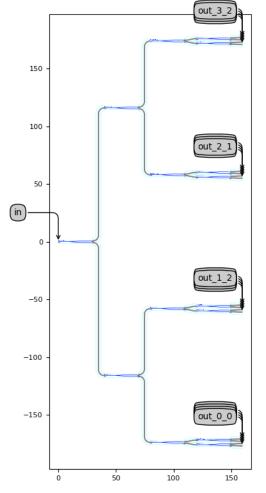

#### Splitter tree (parametric circuit)

#### Spiral waveguide with heater (parametric circuit)

# Matrix of phase shifters (parametric circuit)

# Matrix of grating couplers (parametric circuit)

#### Fully hierarchical – parametric!

4x4 matrix

8x4 matrix

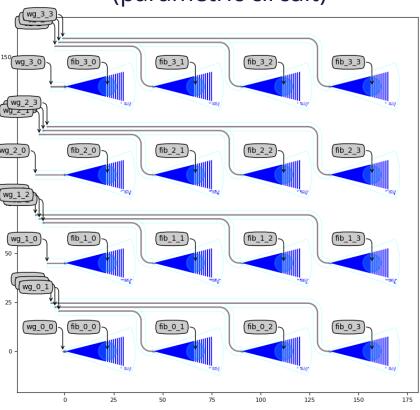

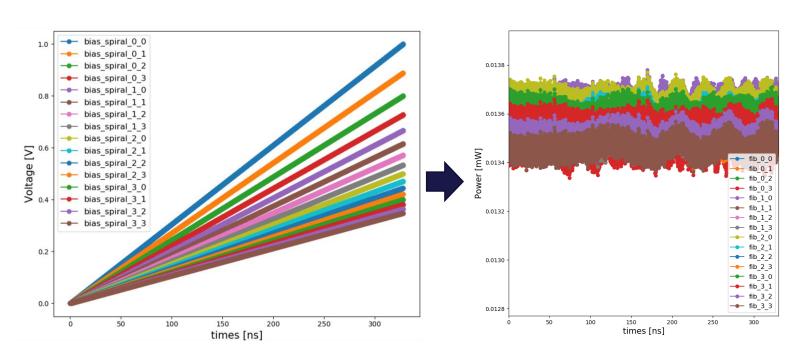

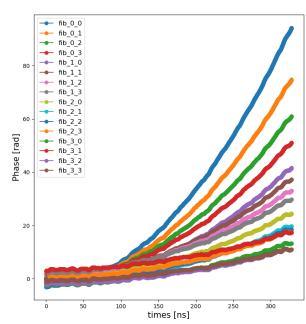

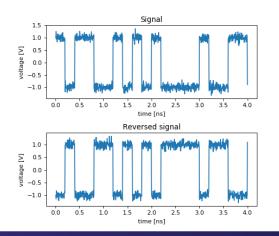

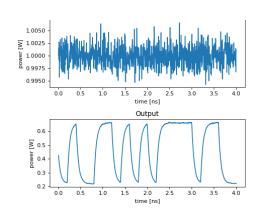

# Circuit model generated automatically! Time domain simulation

Optical power levels of emitted beams function of time

Phase of emitted beams Function of time

for each spiral

Bias voltage as function of time

### Where are we going?

- Even more layout automation

- Simulation & modeling

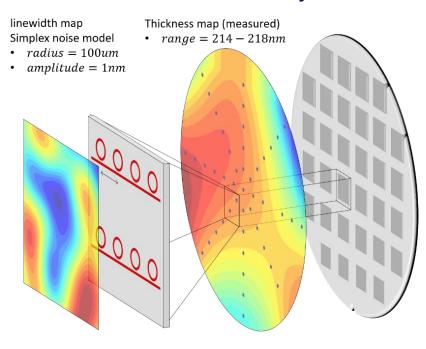

- The chip within the process window: variability analysis

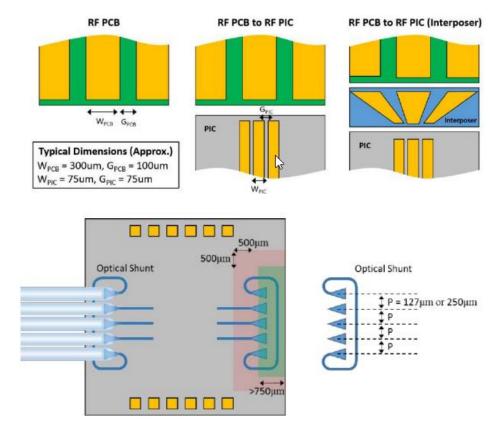

- Off the chip: assembly design kits

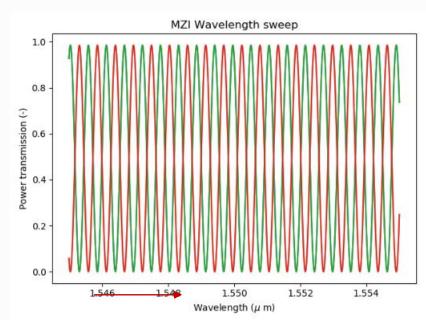

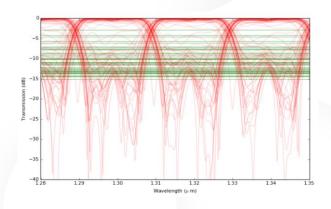

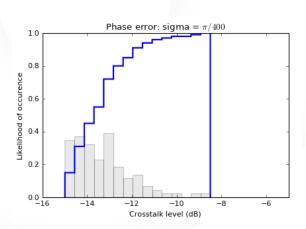

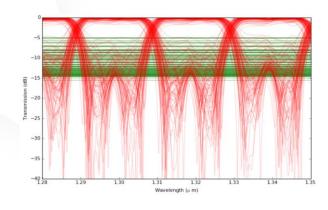

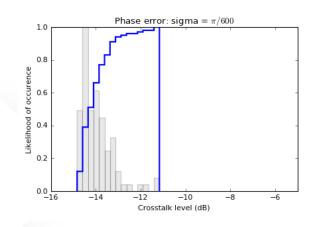

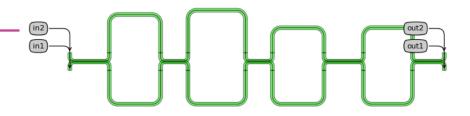

## Variability and yield analysis example

#### Bad phase control

#### Good phase control

#### Cascaded MZI (lattice filter)

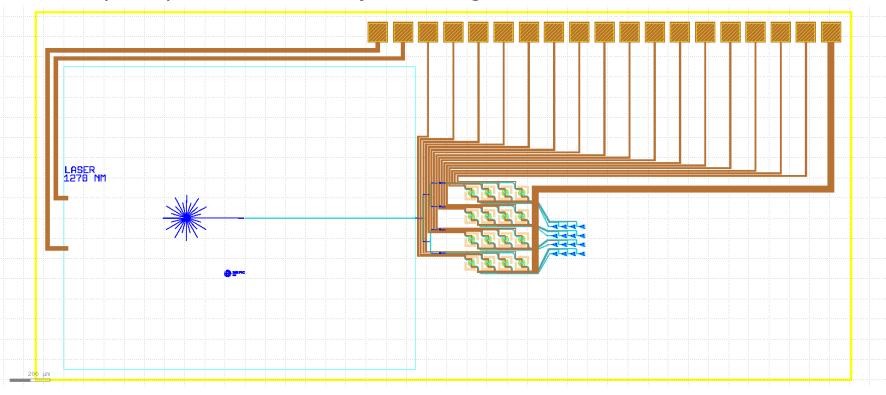

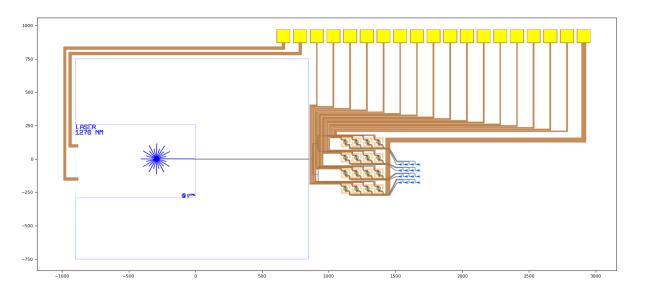

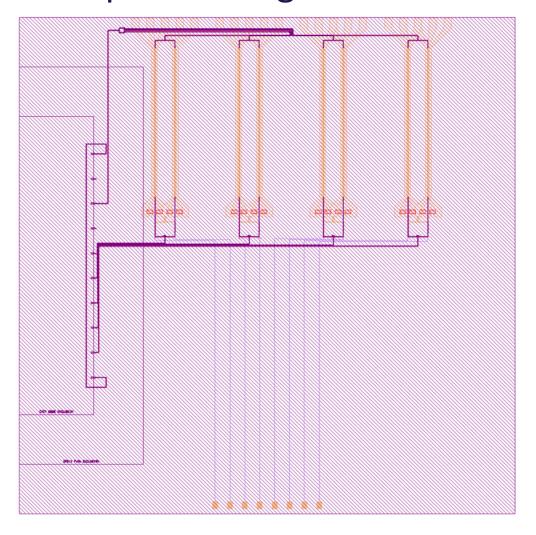

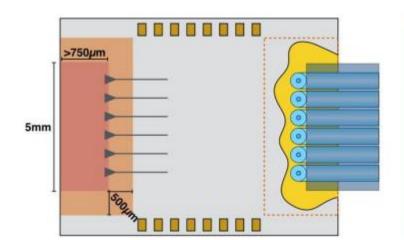

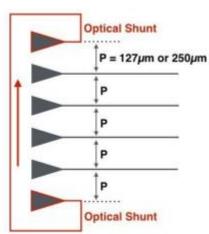

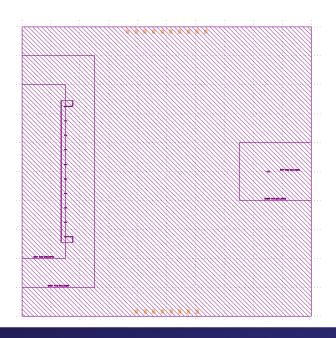

## Example: Packaged 4-Lane Modulator

#### **Respect the packing foundry rules**

```

from si_fab import all as pdk

from tyndall_packaging.all import UniformPackagingArray

packaging_arrray = UniformPackagingArray(

n_o_user_west_gratings=0,

n_o_user_east_gratings=1,

n_o_north_bondpads=10,

n_o_south_bondpads=8,

bondpad=pdk.BondPad(metal1_size=(50, 70), metal2_size=(50, 70)),

grating=pdk.FC_TE_1300(),

)

packaging_array_lv = packaging_arrray.Layout()

packaging_array_lv.write_gdsii("sifab_chip_package_oband.gds")

```

#### Simulate including interface models

# Collaborate?

- Statistical models and PDK creation

- Circuit simulation for novel applications

- Heterogeneous integration, assembly and test