## Silicon Photonics Platform: Current and Future Trends

Philippe Absil, VP R&D

**EPIC Meeting on CMOS Compatible Integrated Photonics at imee**

## Imec Leuven

#### Hyperspectral imaging lab & demo room

Integrated imagers lab

Smart sensor lab

Exascience lab

#### **RF & high-power lab**

-116.388 8

**Photonics labs**

#### 200mm cleanroom

- Silicon pilot line for prototyping and low-volume manufacturing

- iSiPP200 and iSiPP50G photonics prototyping platform

- 200mm GaN-on-Si platform

- Quantum computing lab

- 5,200m<sup>2</sup>

#### GaN Lab

NERF labs

Measurement & testing lab

Material and device characterization labs

#### 300mm cleanroom

- (High-NA) EUV, Attolab, advanced patterning

- State-of-the-art etch, implant, cleaning, metrology, deposition, ... equipment from leading-edge OEMs

- Ballroom type of cleanroom (7,200m<sup>2</sup>, Class 1,000)

- 24/7 operational

Bio labs

- Cell & tissue culture labs

- Optical labs

- Wet chemistry labs

- Clinical labs

- Pre-PCR lab

- Neuropixels lab

WORLD-CLASS INFRASTRUCTURE > 12,000 M<sup>2</sup> CLEANROOM CAPACITY MORE THAN 5,000 SKILLED PEOPLE FROM OVER 95 NATIONALITIES A TRUSTED PARTNER FOR COMPANIES, STARTUPS & ACADEMIA

# Silicon Photonics Has Become An Industrial Reality

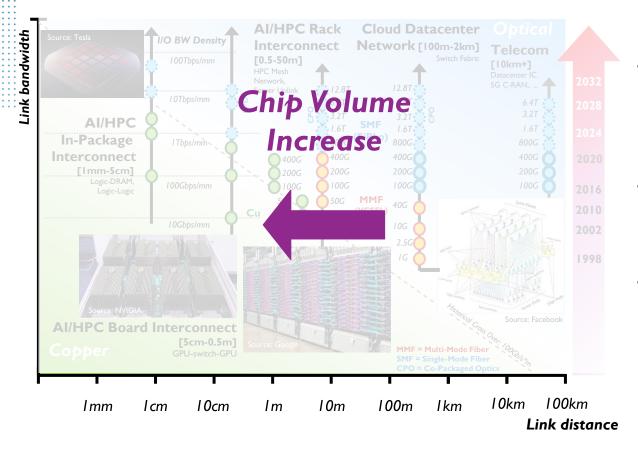

# **Optical Interconnect Landscape and Roadmap**

- Multi-Terabit/s Optical Interconnectivity needed by mid 2020's, driven by Cloud and AI/HPC

- Optical Interconnects will move into the rack, board and package

- Silicon Photonics is a key enabling technology for Terabit-scale Optical Interconnects, from I cm to 100km+

## Silicon Photonics Benefits

- + Chip level integration of various photonic functions

- + Integration of complex optical functions (passive / active)

- + Large-scale integration

- + Integration electronics and photonics

- + Wafer-scale processing using existing CMOS-fabs

- + CMOS-shared Production Infrastructure

- + Focus on one common technology

- + Re-use of advanced CMOS development

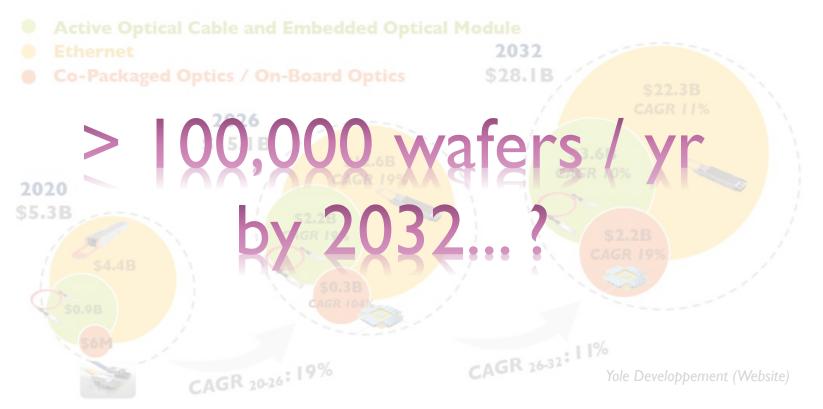

# Datacom Optics Revenue Growth Forecast

The market driven by 1.6T and 3.2T optical engines

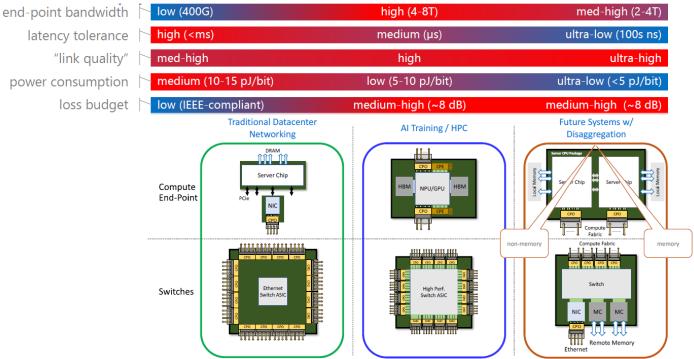

# **Optical Interconnect Requirements**

## Specific to the Application

#### Reference: M. Filer (Microsoft), APPA E Phase 2 Kick

ARPA-E Phase-2 Kick-Off Meeting, Jan 2021

• AI/HPC and System Disaggregation have the most demanding optical link specifications

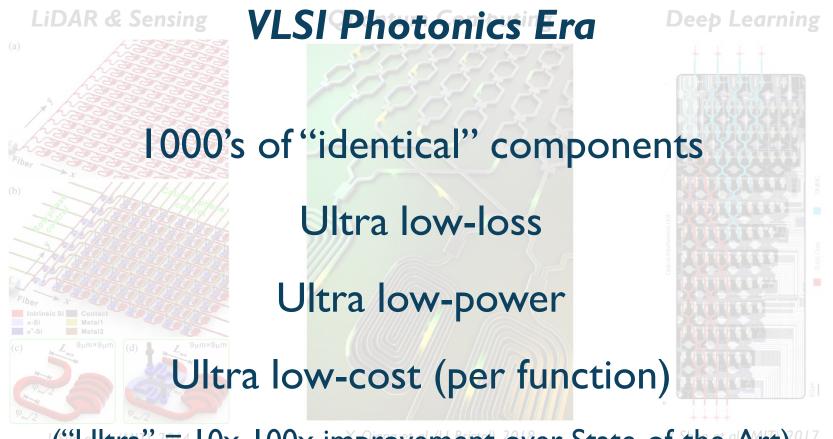

## Emergence of new applications

("Ultra" = 10x-100x improvement over State-of-the-Art)

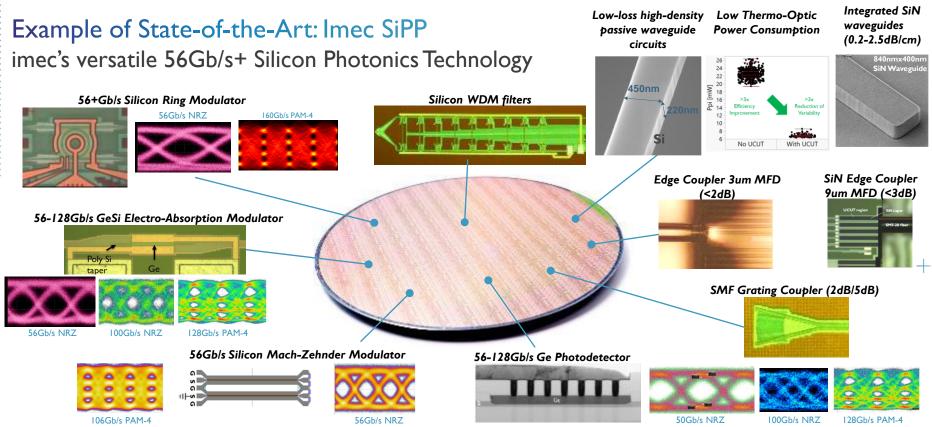

## Current State-Of-The-Art

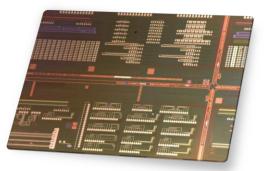

### Fully Integrated Silicon Photonics Platform for 1310nm/1550nm Wavelengths

- Low-loss Passive Silicon Waveguide Devices and Fiber Coupling Structures

- 56Gb/s+ (Ge)Si Modulators and Ge(Si) Photodetectors

# PIC Technology Challenges

### **Photonics** PPAC Challenges

12

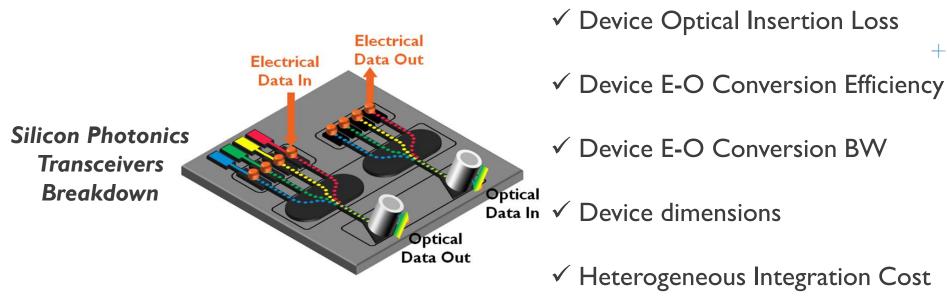

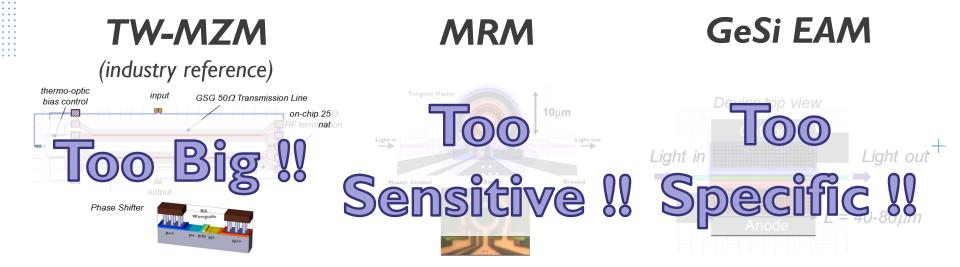

# E-to-O Conversion: The Optical Modulator

"Conventional Approaches"

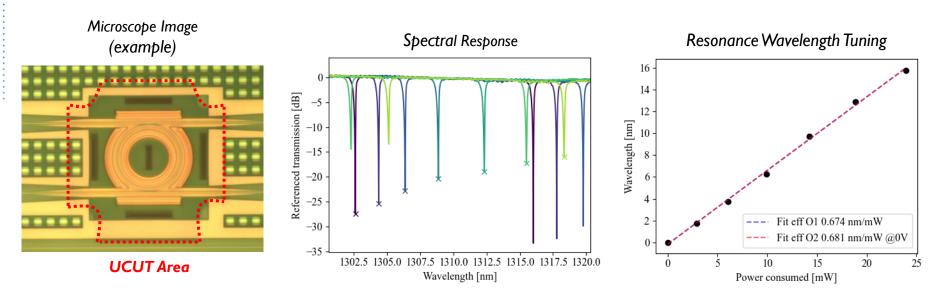

# **Silicon Ring Modulator**

High-Efficiency Heaters with Si Substrate Undercut (UCUT)

High-Speed Si Ring Modulator with **Undercut Si Substrate** achieves 0.68nm/mW or II8GHz/mW thermal tuning efficiency

Defectivity < 500ppm (pre-packaging sorting)

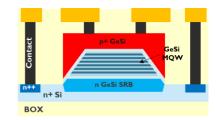

# **O-band GeSi Electro-Absorption Modulator**

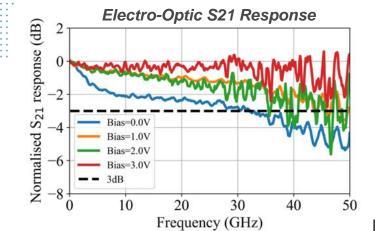

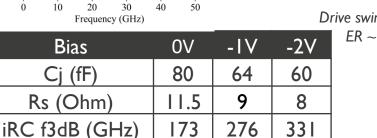

QCSE-EAM: High-Speed Performance

Electrical S11 Response

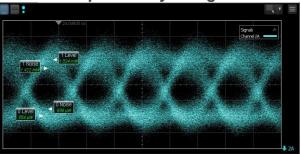

### 60Gbps NRZ Eye Diagram

Drive swing = 2Vpp ER ~ 2.5dB

- Modulation bandwidth  $f_{3dB} \sim 50GHz$  (from 50 $\Omega$ )

- Capacitance C<sub>i</sub><80fF, intrinsic RC bandwidth f<sub>RC</sub>>>100GHz

## **Other Modulator Alternatives**

- Graphene integration (and other 2Ds)

- III-V epitaxy (optically pumped devices + detectors, not yet lasers I assume)

- Alternative EO-materials

+

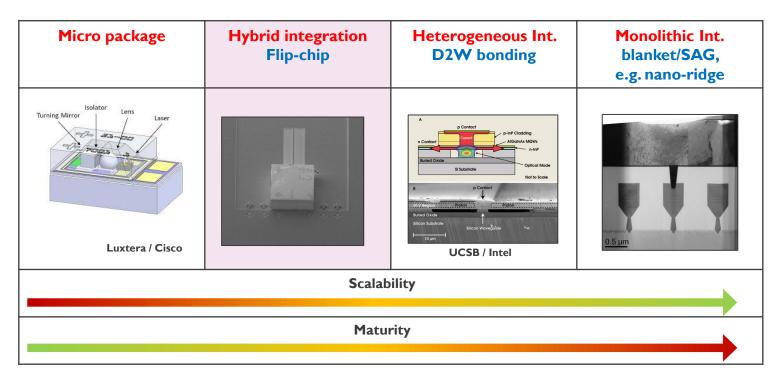

## Laser Integration onto Silicon Photonics PIC

+ Various approaches in development or production

...

+

- Imec short term plans: Flip-Chip Laser "Passive" Assemblies

- Imec long term plans: Heterogeneous III-V layer transfer or Monolithic Integration

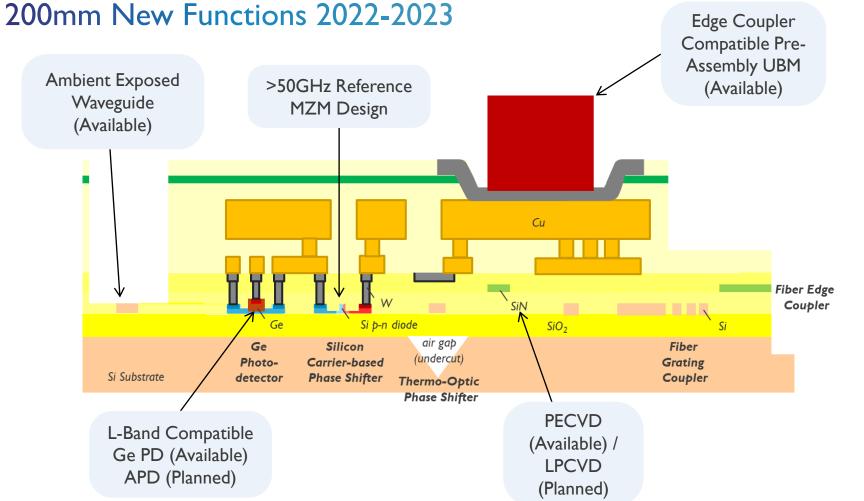

## Imec Silicon Photonics Platform

**Future Trends**

+

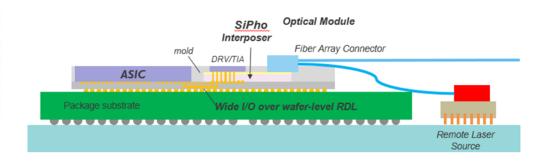

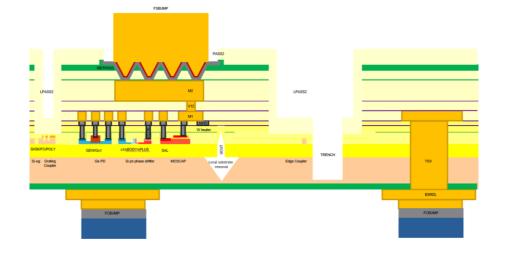

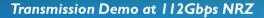

## Upscaling to 300mm – Silicon Photonics Interposers For CPO

### 300mm Key Differentiators

- + Sub-100nm Feature Size (193-*i* litho)

- + nm-scale Process Control

- + 3D assemblies (TSV, μBumps, Hybrid bonding)

# Al-Driven "Inverse" Design

### Example: Polarization Splitter

## "Traditional" Design

Typical Minimum Line / Space ~150-200nm Somewhat Regular Shapes "Inverse" Design

Vuckovic's group (Stanford)

Typical Minimum Line / Space <100nm Irregular Shapes

New patterning requirements !

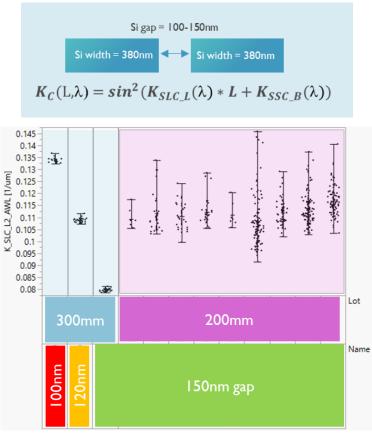

## Waveguide Device Process Control

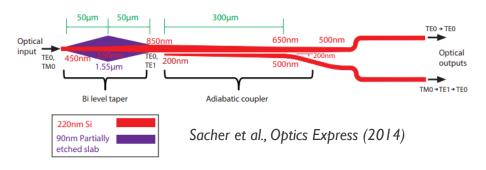

### Silicon Directional Coupler

- + 5-10x reduction in wafer variability

- + Yielding 100nm Si gap

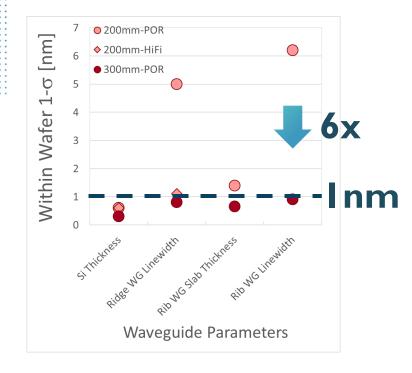

## Waveguide Technology with Sub-nm Control – 300mm

10

$\begin{array}{l} \textbf{Modulator} \ \lambda_{\text{resonance}} \\ \textbf{I-\sigma} \thicksim \textbf{0.9} \ \textbf{nm} \end{array}$

Center Wavelength [nm] @ 0.0V

## 3D EIC-PIC: 40Gb/s TSV-Enabled Silicon Photonics

## I 4nm Foundry FinFET CMOS Drivers,TIA's

imec SiPP300, with TSV

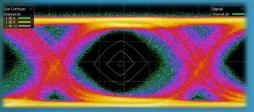

40Gb/s NRZTX eye

D. Guermandi et al., ECOC 2019

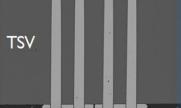

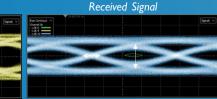

### 40Gb/s NRZ RX eye

50 µm pitch – Flip-Chip Assembly

Launched Signal

# Conclusions

Silicon Photonics is an industrial reality, in the critical path of Datacenters and AI scaling

Advanced CMOS Processing & Heterogeneous Integration will be necessary to address the (Si) photonics scaling challenges