### **LIGENTEC Snapshot**

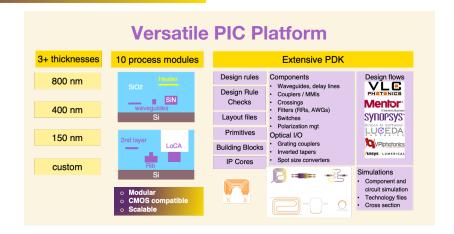

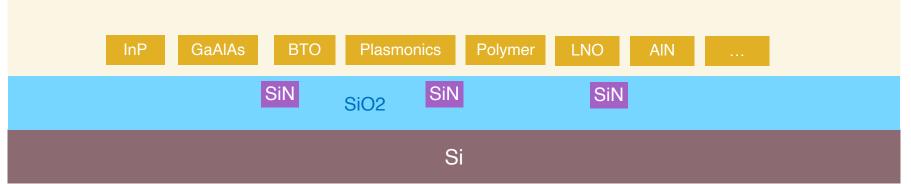

### One base – many options:

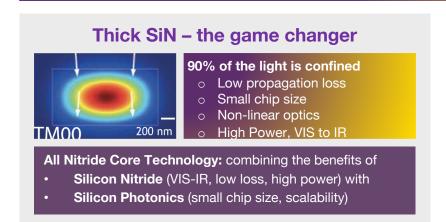

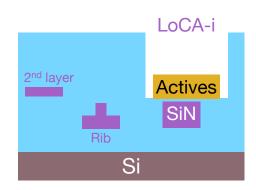

#### Use SiN as base platform for general circuitry

- Comprehensive PDK

- Standard I/Os

- Scalable to volume

Add materials as required by application

#### Focus on wafer level integration e.g.:

- Monolithic integration

- Wafer bonding

- Micro Transfer Printing

### **Integration Technologies**

# **Monolithic** Integration **Deposited** or grown on the wafer

- Best cost option potential

- Performance trade-off

- Limited material choice

- Mature for same platform materials

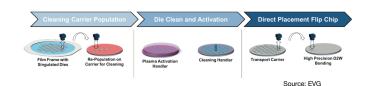

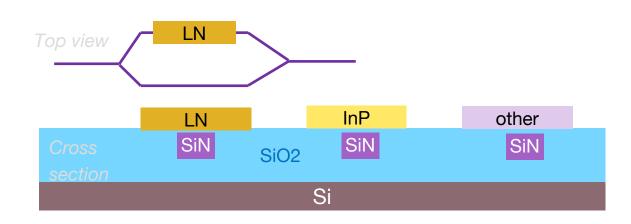

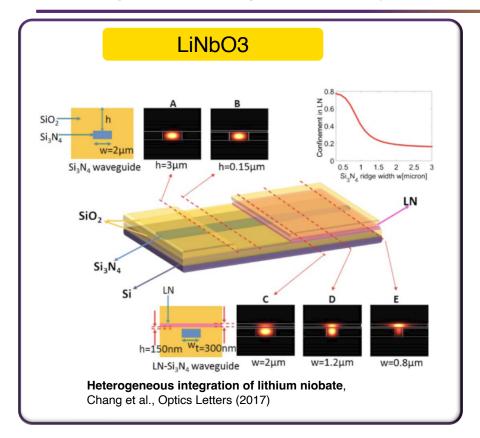

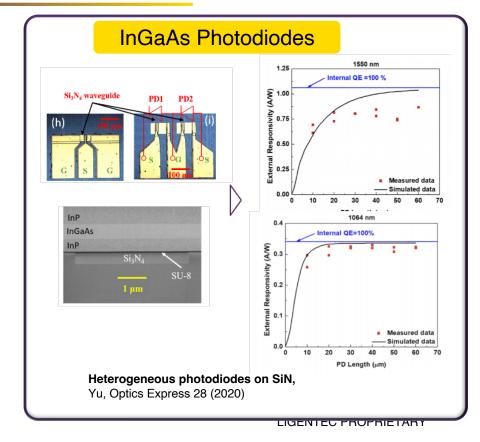

## **Heterogeneous** Integration **Transferred** / bonded on the wafer

- High material integration flexibility

- Best material per application

- Low cost potential

- Emerging technology

# **Hybrid** Integration **Assembled** in the package

- High flexibility

- KGD integration

- Packaging complexity

- Costly in volumes

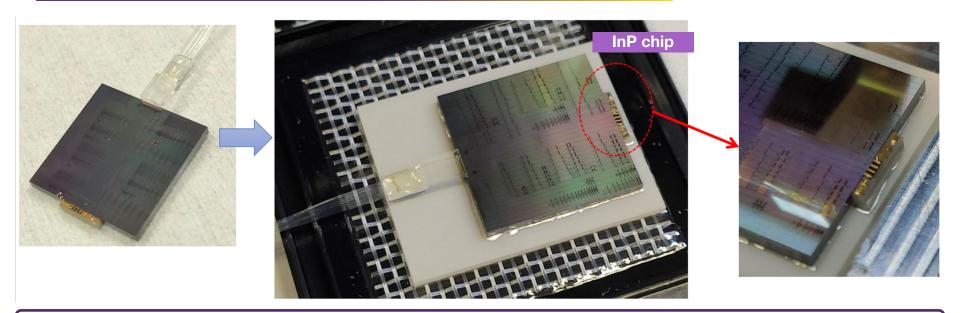

# Hybrid Integration example InP Chip to passive SiN PIC

- SiN chip with FAU and SOA attached to it

- Assembly is glued on a ceramic carrier

- Requires flat and smooth chip facets

### **Heterogeneous Integration**

## Chip to Wafer

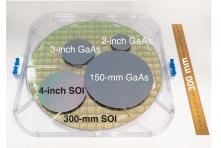

### **Wafer to Wafer**

- Thermal budget, after material transfer, is reduced → increased propagation losses or new material

- Yield of combined stack is reduced (Yield<sub>SiN</sub>\* Yield<sub>active</sub>\* Yield<sub>integration</sub>) → preference to test both active and SiN

- Wafer size not always available for W2W integration in photonics

### LIGENTEC platform

## **Heterogeneous Integration examples**

# Thanks to all Ligentec Team

LIGENTEC