SL.

-

# Assembly & Test

## ALEXANDER JANTA-POLCZYNSKI

SENIOR ADVANCED PACKAGING ENGINEER

ajantapo@ca.ibm.com

# **North American Assembly and Test Provider**

## Packaging & test solutions

- Advanced Flip Chip & Photonics

- Any wafer source

- "Masters of Complexity"

- Outstanding characterization

- Design for manufacturing/Test

- OSAT > 40 yrs of experience

#### **Market Segments**

HPC HPC HPC HPC Herospace Defense Herospace Defense Herospace Defense

#### Advanced & Complex Package

• Design  $\rightarrow$  prototypes  $\rightarrow$  HVM

#### **Efficient & Effective Production**

- Low/High Volume

- High mix environment

## Better Time to market

IBM Assembly and Test 2021

REDEF NING HE LIMITS

# **IBM Bromont – Advanced Packaging**

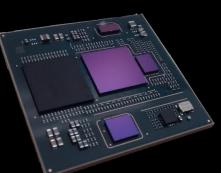

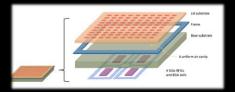

Heterogenous integration of various node function in SiP

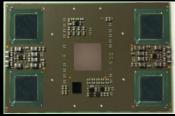

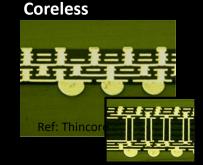

## Large MCM

## Large SCM/DCM

#### MCM - HI / SiP

Custom

CSP

2.1D/2.3D

2.5D

3D

Photonics

📣 IBM presentation

4

#### REDEF NING HE LIMITS

# System in Package

## **FC-PBGA SIP solutions**

**Board level integration**

$\rightarrow$  Cost reduction

Mixing device technologies at package level provides:

- Very close die & components positioning

- Higher bandwidth and lower power

- Better signal integrity

- Smaller system level footprint

- Modularity for cost savings

- ightarrow Next generation component drop-in

#### SIP in high volume production

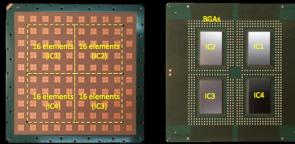

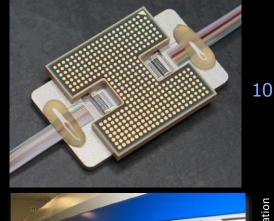

# Antenna on Package

### 5G radio access application AoP SIP

- phased-array antenna-in-package module

- 64 dual-polarized elements

- Package size 70 x 70 mm

- Tight spacing control in assembly

- over 50dBm EIRP in TX mode

- ±40 degrees scanning range

#### Assembled phased array with four transceiver ICs showed

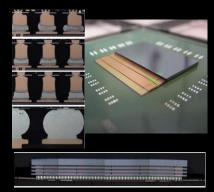

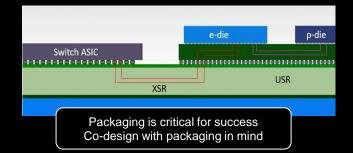

# **Co-Packaging – Advanced integration**

Disaggregation  $\rightarrow$  Package integration Heterogenous integration of various node function in SiP

Simulation

Design

Substrate

Manufacturability

**Optical Performance**

Electrical Performance

Reliability

Industry 4.0

Modeling

Measure & Test

**Thermal Management**

\$

Cost / yield

Predictive manufacturing

6

-joo

IBN.

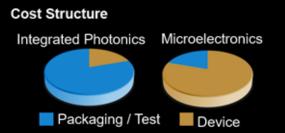

# **Silicon Photonic Packaging Vision**

REDEFINING HE LIMITS

## Lowering packaging cost Increased scalability

- Active alignment

- One connection at a time

- Custom design

# Manual / Low volume — Automated / High volume

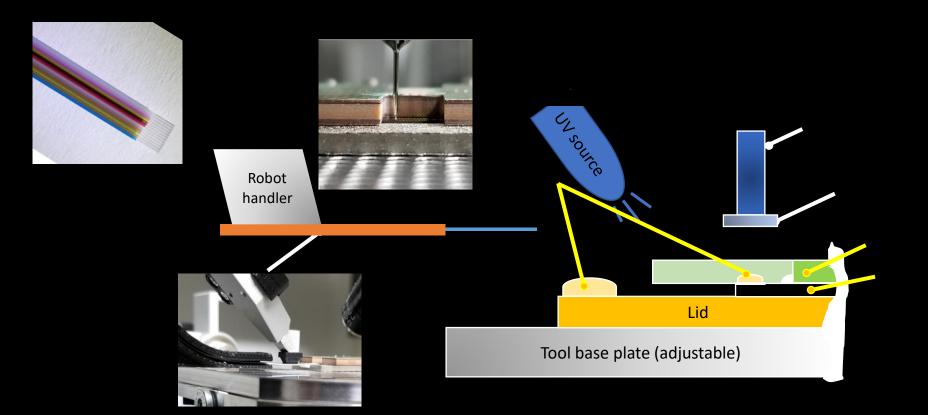

- Self alignment

- Multiple connections at a time

- Standard design

Leverage Microelectronic Packaging Infrastructure / Knowhow

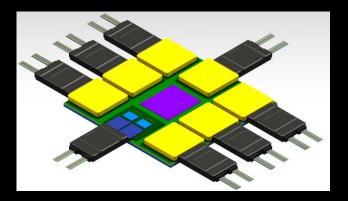

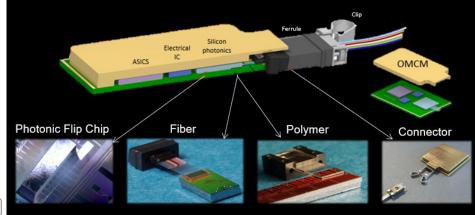

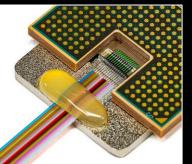

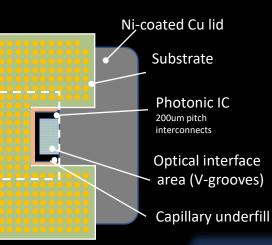

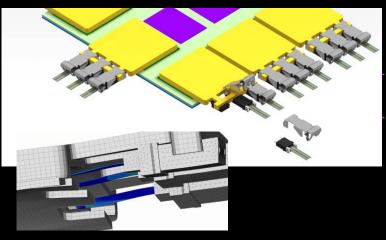

### Typical 2D Multi-Chip Module package with integrated optics

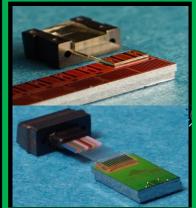

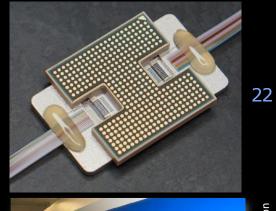

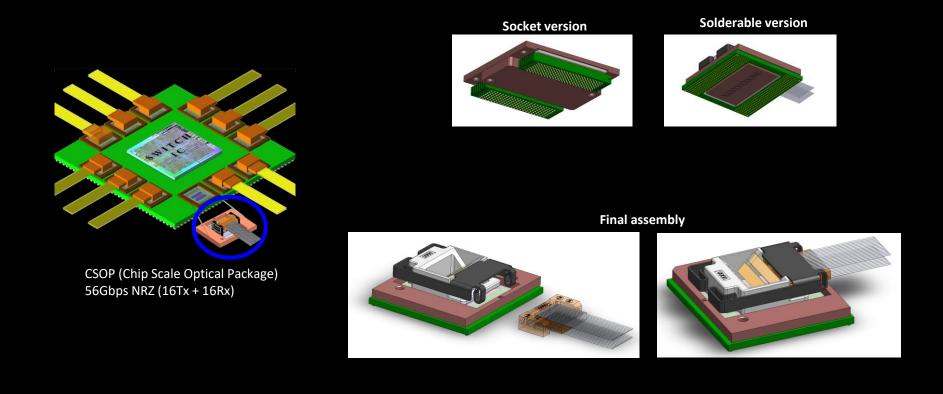

# **Photonic co-packaging demonstrator**

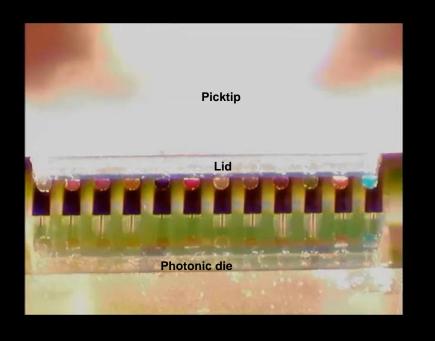

MT ferrule attached to CSOP lid

MT ferrule part

REDEFINING HE

#### **High Fiber Counts Application**

#### **High Density Optical Port Counts Application**

#### **Integrated Connector**

of fiber cable to be plugged in

#### Clip installed during fiber cable plug in

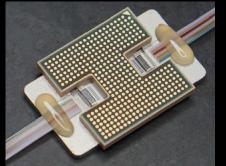

#### Solder Reflowable Silicon **Photonics Fiber assembly**

### Strain Relief of fiber assembly pigtail

#### **PIPES Transceiver**

#### **Full Optical Switch**

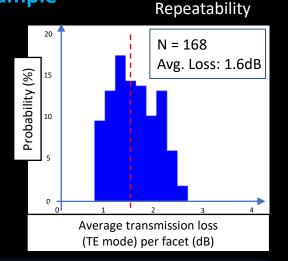

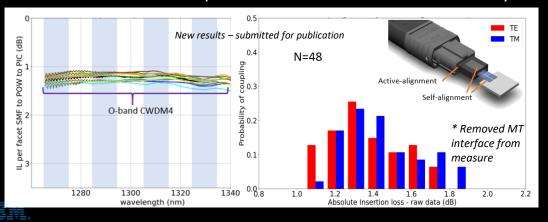

# Fiber Array – Single mode solder reflowable coupler

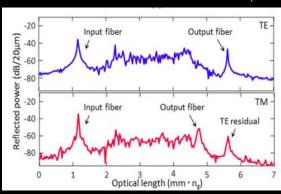

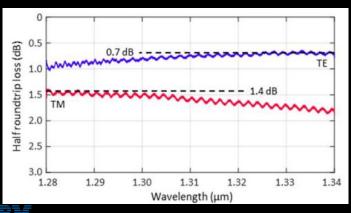

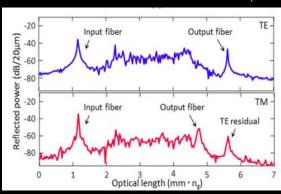

Parallel channel array (12ch TV) O, S, C, L bands compatible Couples both polarizations (TE / TM) High throughput pick n place tools Solder reflow compatible (260 C)

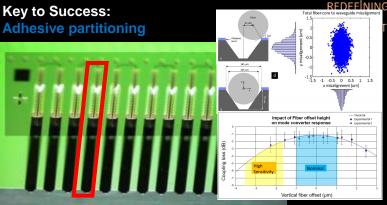

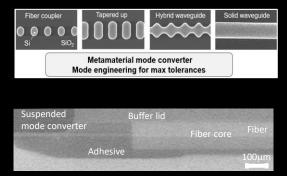

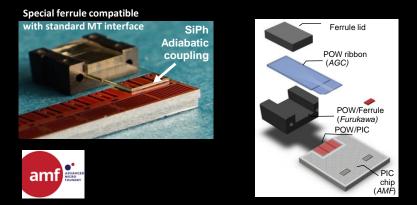

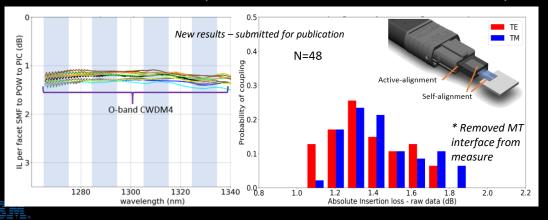

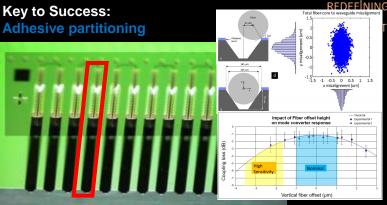

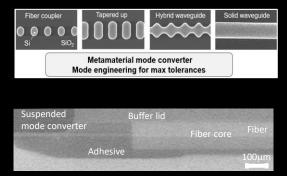

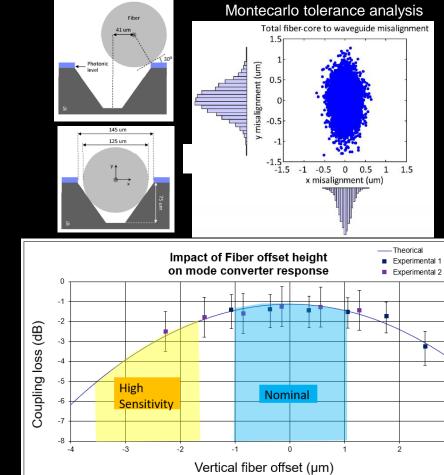

### **Integrated Metamaterial Interfaces for Self-Aligned** Fiber-to-Chip Coupling in Volume Manufacturing

IEEE Journal of Selected Topics in Quantum Electronics Volume: 25, Issue: 3, May-June 2019

#### Structural adhesive for fiber

- Mechanical stability/robustness Fast UV tack (< 5 sec)</li>

- Optical adhesive for suspended region: Optical performance

- Reduce stress on fragile membrane

Fiber ribbon assembly in V-grooves (X-ray tomo)

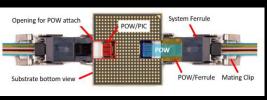

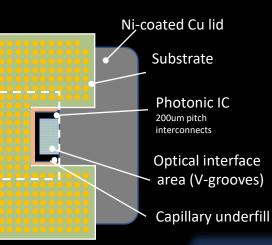

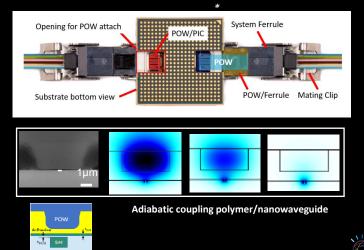

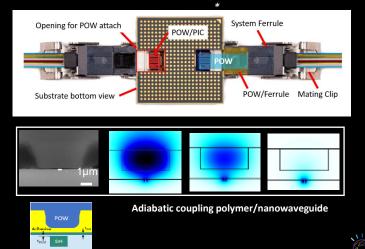

## Photonic Flip-Chip assembly example

Bottom view substrate side of the module

Formic acid flip-chip bonding

Fluxless solution required to maintain grooves/facet cleanliness and SWG integrity

Fluxless formic acid reflow with temporary adhesive material (tacking fluid)

No voiding / cracking of the IMC & solder

Formic acid reflow available at IBM Bromont

IEEE 70th ECTC 2020

IBM presentation

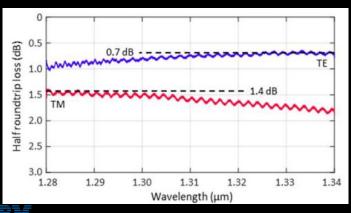

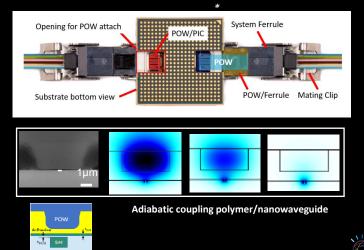

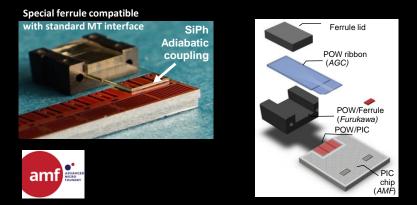

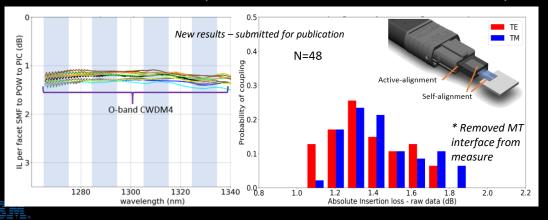

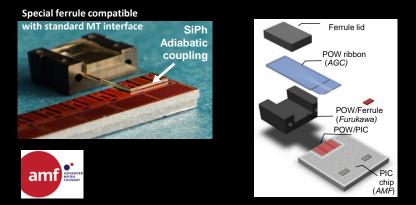

## **Compliant Polymer interface – Dense Single mode coupler**

JSTQE 2020 REDEF NING \*ECOC2020 IMITS

Parallel channel array (dense 50µm pitch – 12ch TV) O, S, C, L bands compatible Couples both polarizations (TE / TM) Assembly using high throughput pick n place tools

- Denser pitch (up to 25µm) at chip interface

- No need for deep grooves (wet etch process)

- Mode converter structure is simple

- Compliant material for CPI risk mitigation

Advances in Interfacing Optical Fibers to Nanophotonic waveguides via Mechanically Compliant Polymer Waveguides IEEE Journal of Selected Topics in Quantum Electronics - 06 January 2020

# Offer

# Expertise

- 7nm

- Proven material sets for high performance

- Prototyping to high volume manufacturing

# Time to market

Benefit from existing models and designs to accelate MCM implementation

Beyond groundrules:

Customization

Characterization

# Business Model

Co design partners

Streamlined manufacturing flow

Integrated supply chain

IBM presentation

13

We put our packaging know how at your service Focusing on your application and performance

14

IBM presentation

-00

# IBM Packaging and Test www.ibm.com/assembly

# Thank You We are here for you!

ajantapo@ca.ibm.com

## **HDI with Photonics**

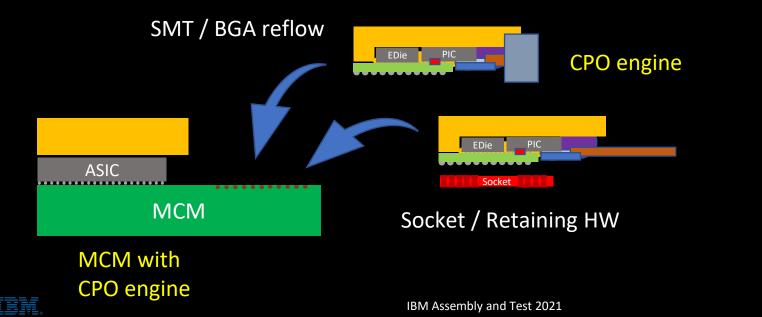

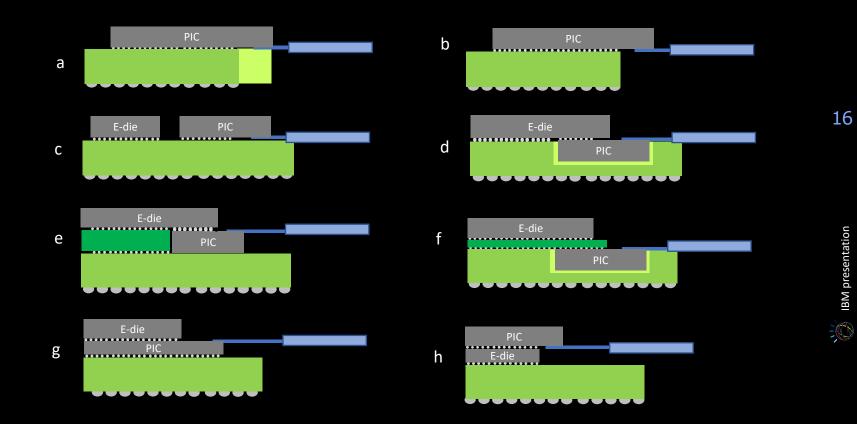

# **Co-packaged Optics Configuration examples**

#### REDEF NING HE LIMITS

# **Co-Packaging in Advanced integration**

IBM.

# Fiber Array – Single mode solder reflowable coupler

Parallel channel array (12ch TV) O, S, C, L bands compatible Couples both polarizations (TE / TM) High throughput pick n place tools Solder reflow compatible (260 C)

### **Integrated Metamaterial Interfaces for Self-Aligned** Fiber-to-Chip Coupling in Volume Manufacturing

IEEE Journal of Selected Topics in Quantum Electronics Volume: 25, Issue: 3, May-June 2019

#### Structural adhesive for fiber

- Mechanical stability/robustness Fast UV tack (< 5 sec)</li>

- Optical adhesive for suspended region: Optical performance

- Reduce stress on fragile membrane

Fiber ribbon assembly in V-grooves (X-ray tomo)

## **Compliant Polymer interface – Dense Single mode coupler**

JSTQE 2020 REDEF NING \*ECOC2020 IMITS

Parallel channel array (dense 50µm pitch – 12ch TV) O, S, C, L bands compatible Couples both polarizations (TE / TM) Assembly using high throughput pick n place tools

- Denser pitch (up to 25µm) at chip interface

- No need for deep grooves (wet etch process)

- Mode converter structure is simple

- Compliant material for CPI risk mitigation

Advances in Interfacing Optical Fibers to Nanophotonic waveguides via Mechanically Compliant Polymer Waveguides IEEE Journal of Selected Topics in Quantum Electronics - 06 January 2020

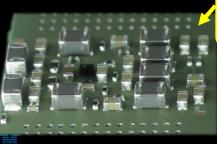

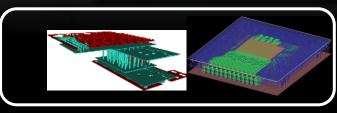

# Deep capability in design, modeling, failure analysis and qualification

"First time right results"

- Predictive and validated mechanical modeling

- Proven electrical modeling, simulation, analysis and characterization refined through empirical authentication

- Demonstrated thermal modeling capabilities confirmed through HVM products

- Innovative photonics single mode packaging and certified OSAT

- Top-of-the-industry failure analysis skills and labs

- Package and Product gualification services complying with reliability standards

HFSS Q3D. 2D. SiWave

PowerSI IBM Internal tools

RFDFF

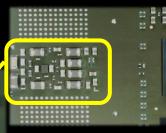

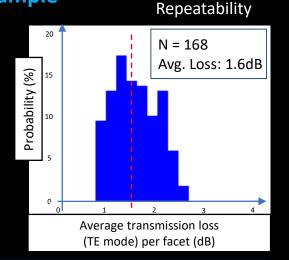

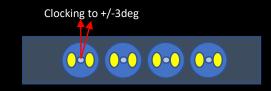

## Fiber Array – Self-alignment

## 10 μm pick and place Self alignment to ~1 μm

## Photonic Flip-Chip assembly example

Bottom view substrate side of the module

Formic acid flip-chip bonding

Fluxless solution required to maintain grooves/facet cleanliness and SWG integrity

Fluxless formic acid reflow with temporary adhesive material (tacking fluid)

No voiding / cracking of the IMC & solder

Formic acid reflow available at IBM Bromont

IEEE 70th ECTC 2020

Formic acid furnace R&D formic acid oven also available

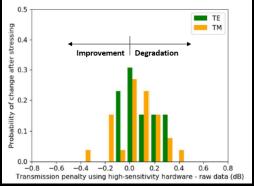

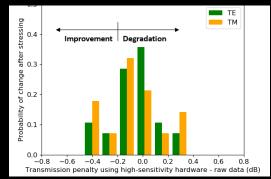

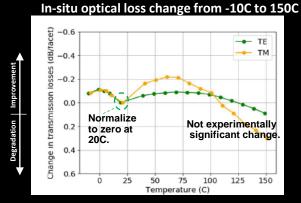

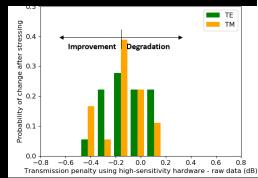

## Fiber Array – Reliability Demonstration

#### Solder reflow (5x) 1min@250C

#### Thermal Cycling -40/85C&-40/125C : total 2000 cycles

#### Damped heat 85C 85%RH : 2000 hrs

Assembly

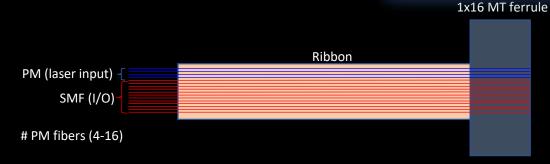

## **Photonic copackage – Optical connectors**

#### What is needed from fiber component suppliers

- Disruptive innovation to reduce connector size (integrated version)

- > Solder reflow compatible ferrules

- Low loss SM 1x16 .. 2x16 ? 1x24?

- SM with 80µm fiber on reduced pitch

- > PM arrays and Combination of PM / SMF fibers

- Efficient shipping and expedition of fiber component and photonic module

ER > 20dB

\* Ideally Integrated connector to be solder reflow compatible

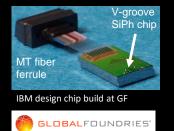

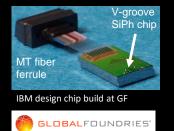

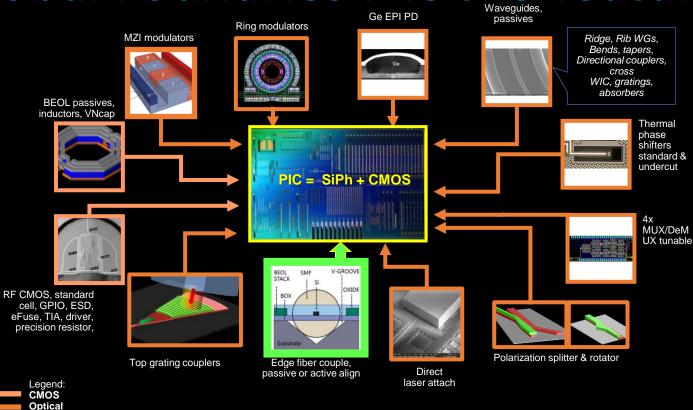

# Global Foundries : 45CLO feature set

*courtesy of GF source IBM-GF : CPO Webinar Sept16,2020*

REDEF NING

# Global Foundries – Chips for co-packaged photonics

|                                           | Electronic technology for<br>hybrid integration |                    |                   | GF monolithic CMOS - SiPh |                  |

|-------------------------------------------|-------------------------------------------------|--------------------|-------------------|---------------------------|------------------|

|                                           | 14FF                                            | 22FDX <sup>®</sup> | BiCMOS            | 90WG                      | <b>45CLO</b>     |

| nMOS Ft                                   | 270GHz                                          | 350GHz             | 500GHz            | 150GHz                    | 280GHz           |

| Supply V                                  | 0.8V                                            | 0.8V               | 3.3V              | 1.2V                      | 1.0V-1.1V        |

| Substrate                                 | BULK                                            | SOI                | SiGe HBT          | SOI                       | SOI              |

| Mx res & rap                              | High                                            | Low                | Very low          | Very low                  | Very low         |

| Parasitic load                            | 5-30fF                                          | 5-30fF             | 5-30fF            | 2-3fF                     | 2-3fF            |

| ESD cap                                   | ~50fF                                           | ~50fF              | ~50fF             | 0                         | 0                |

| Estimated TIA 3dB BW<br>@1k <b>û</b> gain | 24 GHz<br>*(70fF)                               | 28 GHz<br>*(70fF)  | 33 GHz<br>*(70fF) | 35 GHz<br>*(20fF)         | 47GHz<br>*(20fF) |

- RF-grade CMOS FETs integrated with SiPh

- Dense high speed channel integration

- Reduced packaging costs

- ESD elimination further reduces input capacitance

- Significant TIA bandwidth due to low input capacitance

*courtesy of GF source IBM-GF : CPO Webinar Sept16,2020*

## **Compliant Polymer interface – Dense Single mode coupler**

JSTQE 2020 REDEF NING \*ECOC2020 IMITS

Parallel channel array (dense 50µm pitch – 12ch TV) O, S, C, L bands compatible Couples both polarizations (TE / TM) Assembly using high throughput pick n place tools

- Denser pitch (up to 25µm) at chip interface

- No need for deep grooves (wet etch process)

- Mode converter structure is simple

- Compliant material for CPI risk mitigation

Advances in Interfacing Optical Fibers to Nanophotonic waveguides via Mechanically Compliant Polymer Waveguides IEEE Journal of Selected Topics in Quantum Electronics - 06 January 2020

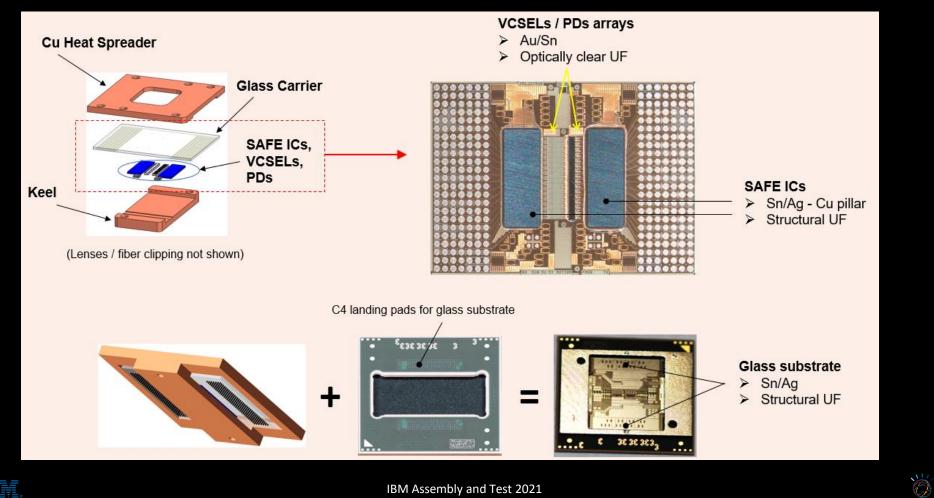

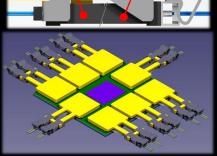

## **ARPA-E Enlighten:** Motion – VCSEL co-packaging

<u>Multi-wavelength Optical Transceivers</u> Integrated On Node

## **ARPA-E Enlighten: Motion – VCSEL co-packaging**